Question

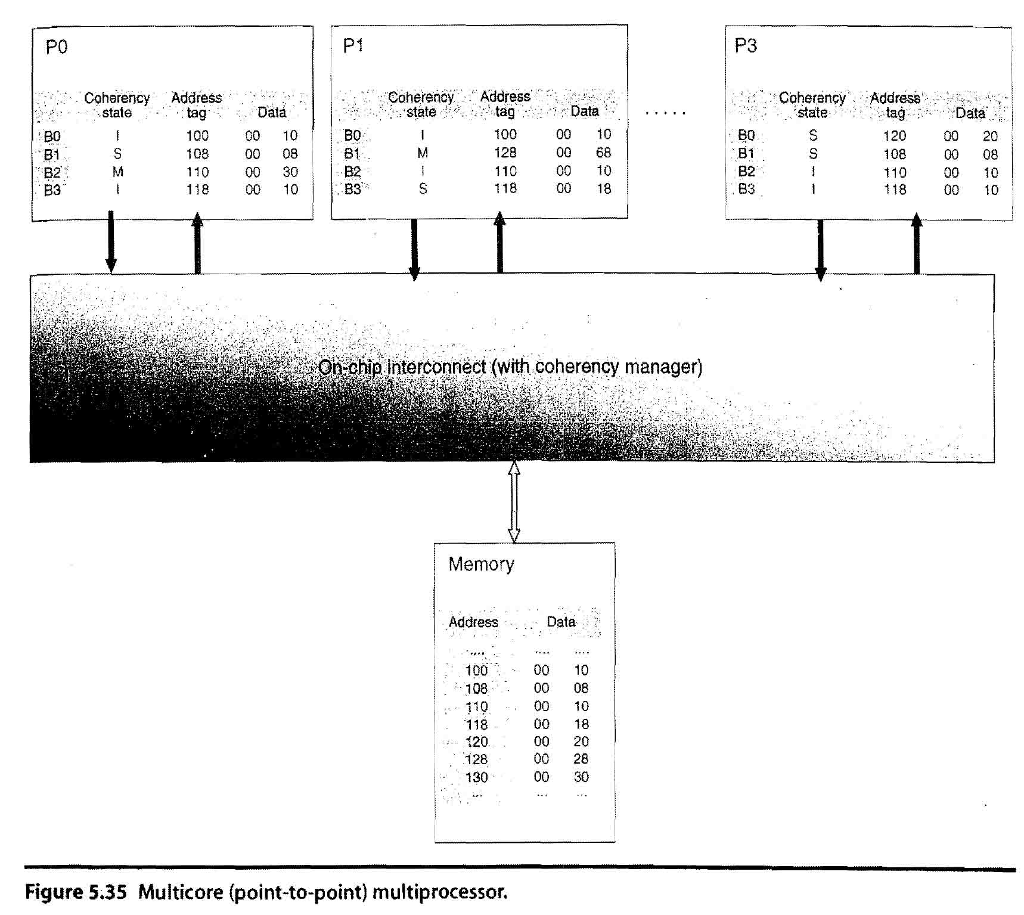

For each part of this exercise, assume the initial cache and memory state as illustrated in Figure 5.35. Each part of this exercise specifies a

For each part of this exercise, assume the initial cache and memory state as illustrated in Figure 5.35. Each part of this exercise specifies a sequence of one or more CPU operations of the form:

P#:

where P# designates the CPU (e.g., P0),

a. [10] PO: read 120

b. [10] PO: write 120

c. [10] P3: write 120

d. [10] P1: read 110

e. [10] PO: write 108

f. [10] PO: write 130

g. [10] P3: write 130

P1 PO Coherency Address state Coherency Address Data Data state tag 100 00 10 B0 100 00 10 128 00 68 108 00 08 B1 B1 00 30 B2 00 10 10 B2 110 118 00 18 B3 B3 118 00 10 Memory Address Data 100 00 10 108 00 08 00 10 10 00 18 118 20 00 20 00 28 128 130 00 30 Figure 5.35 Multicore (point-to-point) multiprocessor. P3 BQ B1 B2 coherency Address state tag Data 120 00 20 108 00 08 110 00 10 18 00 10 P1 PO Coherency Address state Coherency Address Data Data state tag 100 00 10 B0 100 00 10 128 00 68 108 00 08 B1 B1 00 30 B2 00 10 10 B2 110 118 00 18 B3 B3 118 00 10 Memory Address Data 100 00 10 108 00 08 00 10 10 00 18 118 20 00 20 00 28 128 130 00 30 Figure 5.35 Multicore (point-to-point) multiprocessor. P3 BQ B1 B2 coherency Address state tag Data 120 00 20 108 00 08 110 00 10 18 00 10

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started