Answered step by step

Verified Expert Solution

Question

1 Approved Answer

FSM Templates: 1- Mealy Template: 2- Moore Template: Please answer in verilog and include a testbench and waveforms to show that it is working. Objective:

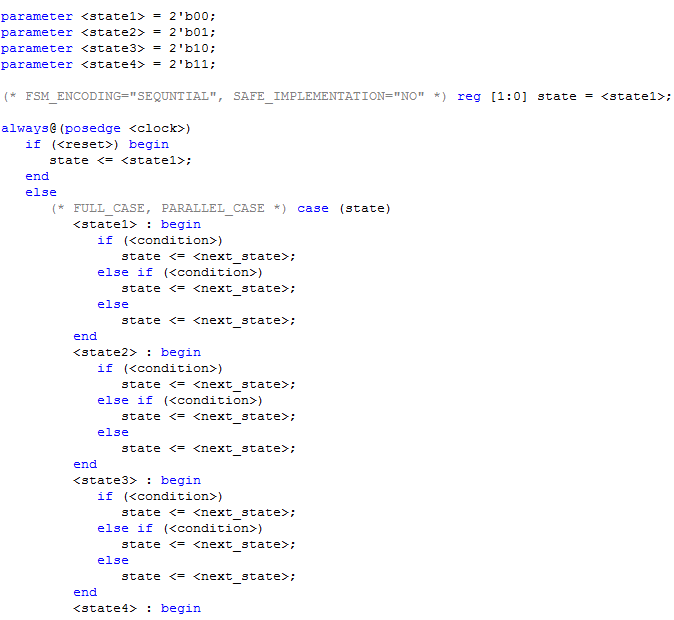

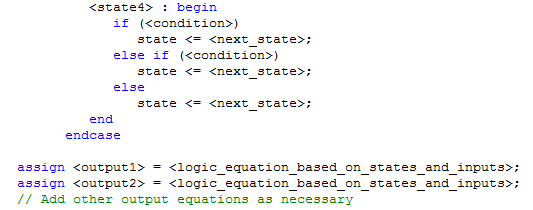

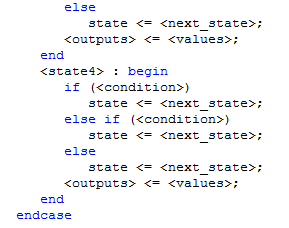

FSM Templates: 1- Mealy Template:

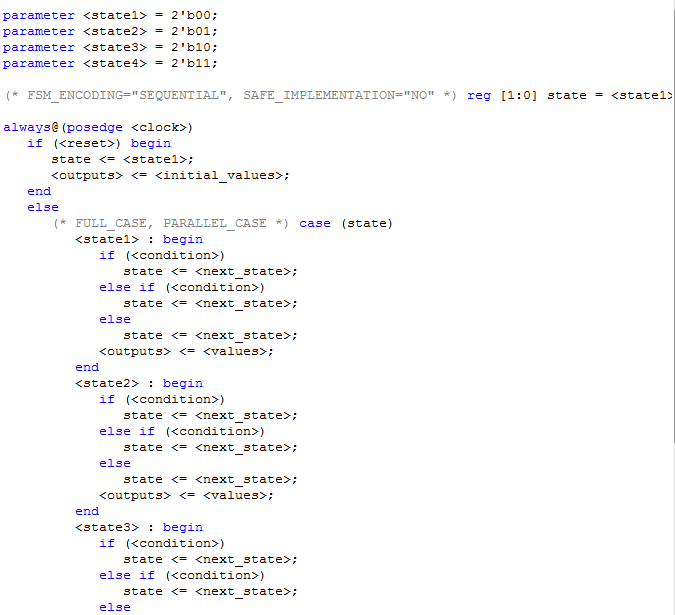

2- Moore Template:

Please answer in verilog and include a testbench and waveforms to show that it is working.

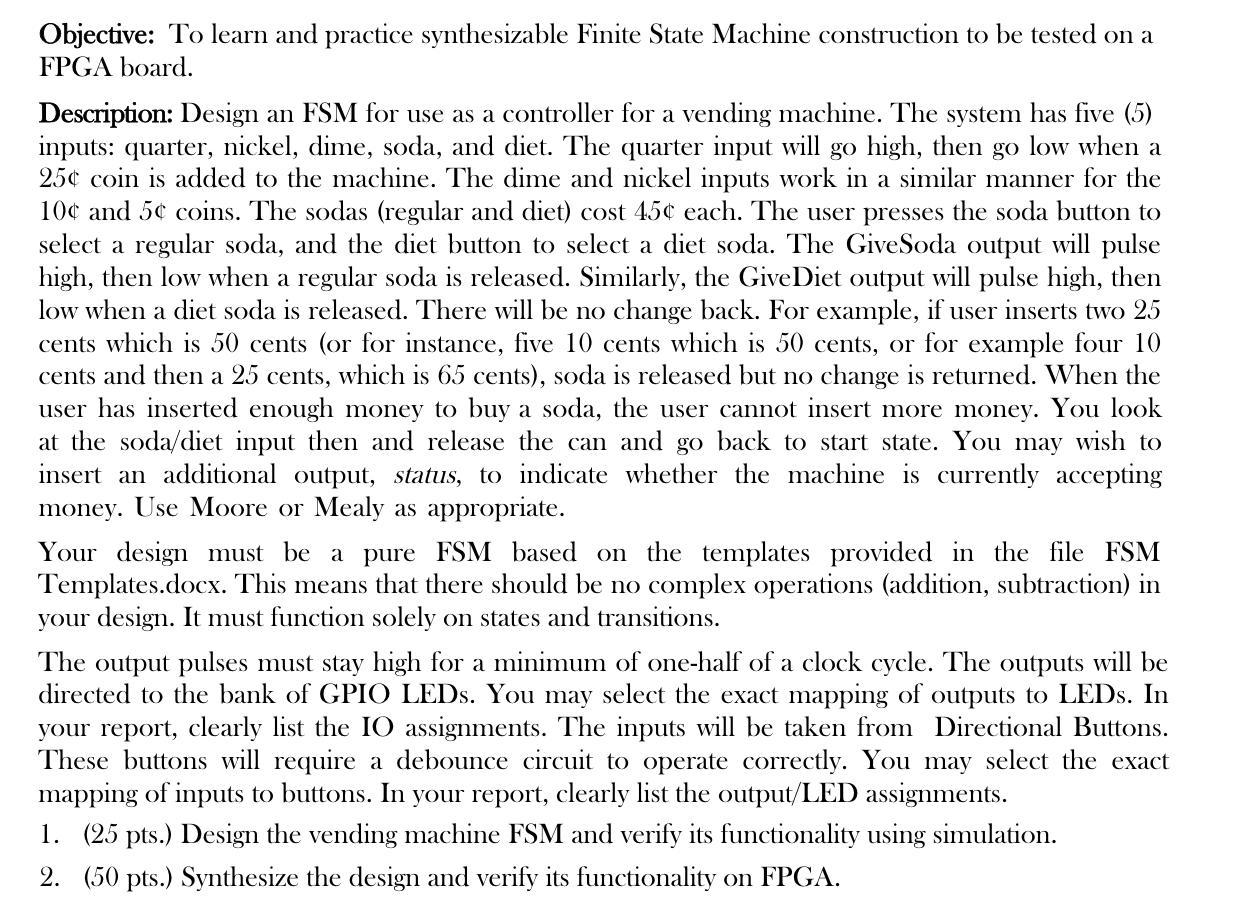

Objective: To learn and practice synthesizable Finite State Machine construction to be tested on a FPGA board. Description: Design an FSM for use as a controller for a vending machine. The system has five (5) inputs: quarter, nickel, dime, soda, and diet. The quarter input will go high, then go low when a 25 coin is added to the machine. The dime and nickel inputs work in a similar manner for the 10 and 5 coins. The sodas (regular and diet) cost 45 each. The user presses the soda button to select a regular soda, and the diet button to select a diet soda. The GiveSoda output will pulse high, then low when a regular soda is released. Similarly, the Give Diet output will pulse high, then low when a diet soda is released. There will be no change back. For example, if user inserts two 25 cents which is 50 cents (or for instance, five 10 cents which is 50 cents, or for example four 10 cents and then a 25 cents, which is 65 cents), soda is released but no change is returned. When the user has inserted enough money to buy a soda, the user cannot insert more money. You look at the soda/diet input then and release the can and go back to start state. You may wish to insert an additional output, status, to indicate whether the machine is currently accepting money. Use Moore or Mealy as appropriate. Your design must be a pure FSM based on the templates provided in the file FSM Templates.docx. This means that there should be no complex operations (addition, subtraction) in your design. It must function solely on states and transitions, The output pulses must stay high for a minimum of one-half of a clock cycle. The outputs will be directed to the bank of GPIO LEDs. You may select the exact mapping of outputs to LEDs. In your report, clearly list the IO assignments. The inputs will be taken from Directional Buttons. These buttons will require a debounce circuit to operate correctly. You may select the exact mapping of inputs to buttons. In your report, clearly list the output/LED assignments. 1. (25 pts.) Design the vending machine FSM and verify its functionality using simulation. 2. (50 pts.) Synthesize the design and verify its functionality on FPGA. parameterStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started