Answered step by step

Verified Expert Solution

Question

1 Approved Answer

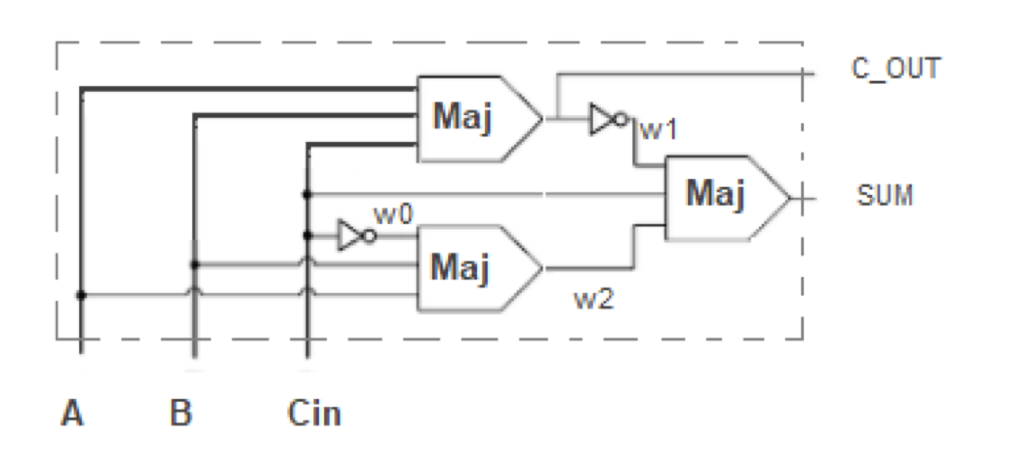

Given the following Full Adder circuit: a) Define a UDP that implements 3-input majority gate (Maj). Assume that the inputs will never take the value

Given the following Full Adder circuit:

a) Define a UDP that implements 3-input majority gate (Maj). Assume that the inputs will never take the value x.

b) Create a Full adder module that uses the UDP designed in (a). Then create a test bench to obtain outputs and waveforms.

C OUT Ma w1 Maj SUM Majw2 A B Cin C OUT Ma w1 Maj SUM Majw2 A B CinStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started