Answered step by step

Verified Expert Solution

Question

1 Approved Answer

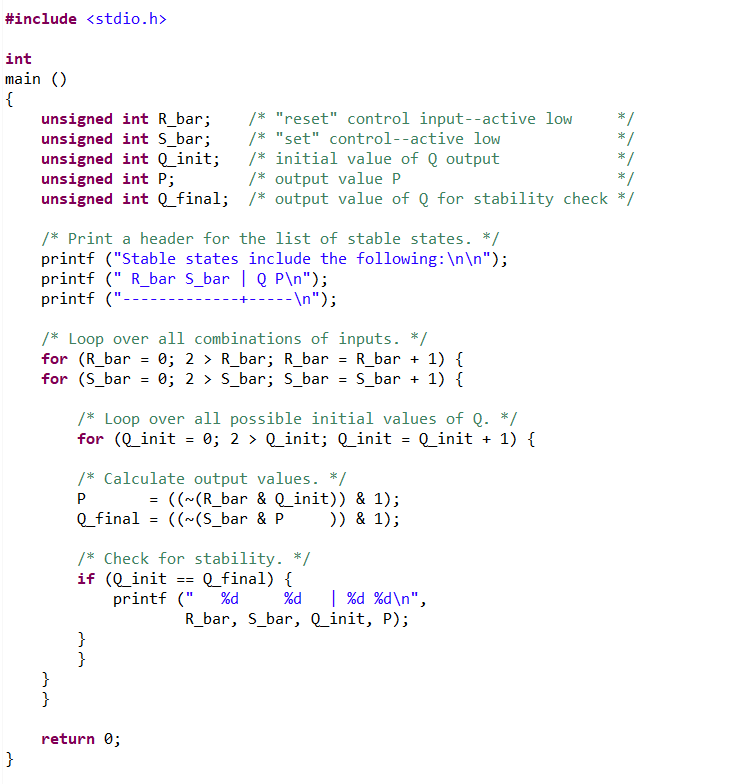

Going to also need some knowledge in electrical engineering to answer. Copy of code: https://pastebin.comdSd9Jj3 Download, compile, and execute the program latch.c. The program finds

Going to also need some knowledge in electrical engineering to answer.

Copy of code: https://pastebin.comdSd9Jj3

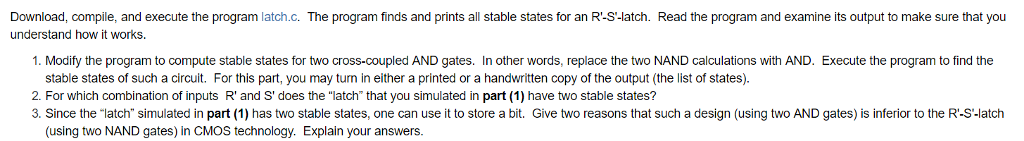

Download, compile, and execute the program latch.c. The program finds and prints all stable states for an R'-S-latch. Read the program and examine its output to make sure that you understand how it works 1. Modify the program to compute stable states for two cross-coupled AND gates. In other words, replace the two NAND calculations with AND. Execute the program to find the stable states of such a circuit. For this part, you may turn in either a printed or a handwritten copy of the output (the list of states). 2. For which combination of inputs R' and S' does the "latch" that you simulated in part (1) have two stable states? 3. Since the "latch" simulated in part (1) has two stable states, one can use it to store a bit. Give two reasons that such a design (using two AND gates) is inferior to the R-S'-latch (using two NAND gates) in CMOS technology. Explain your answers. Download, compile, and execute the program latch.c. The program finds and prints all stable states for an R'-S-latch. Read the program and examine its output to make sure that you understand how it works 1. Modify the program to compute stable states for two cross-coupled AND gates. In other words, replace the two NAND calculations with AND. Execute the program to find the stable states of such a circuit. For this part, you may turn in either a printed or a handwritten copy of the output (the list of states). 2. For which combination of inputs R' and S' does the "latch" that you simulated in part (1) have two stable states? 3. Since the "latch" simulated in part (1) has two stable states, one can use it to store a bit. Give two reasons that such a design (using two AND gates) is inferior to the R-S'-latch (using two NAND gates) in CMOS technology. Explain your answers

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started