Answered step by step

Verified Expert Solution

Question

1 Approved Answer

I. LABORATORY OBJECTIVES The purpose of this short, 1-week lab is to give you some practice with designing como give you some practice with designing

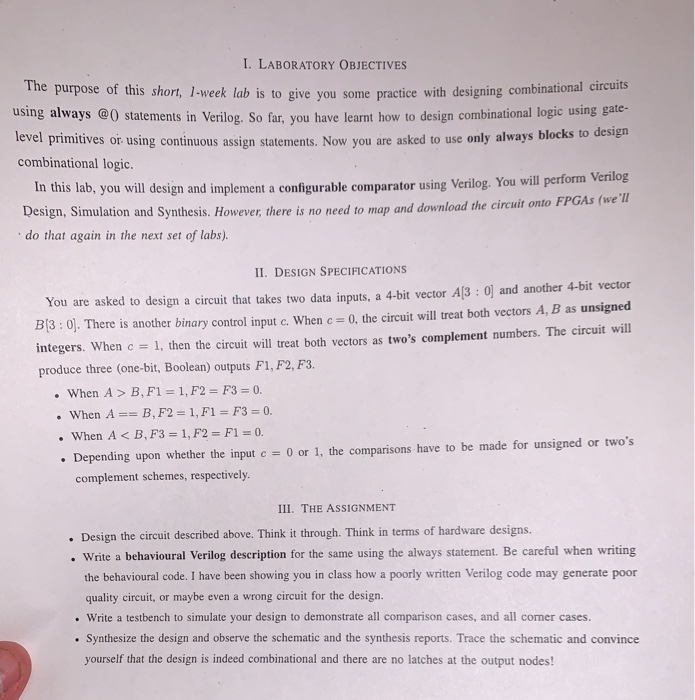

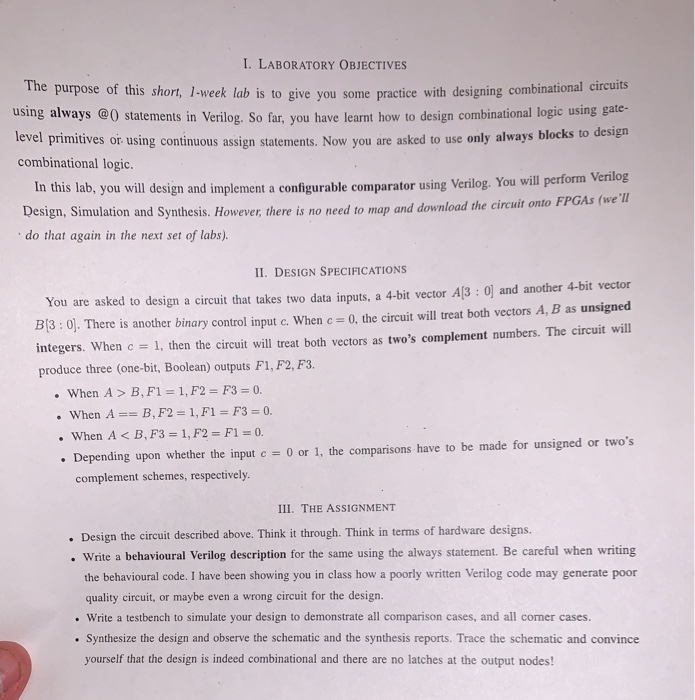

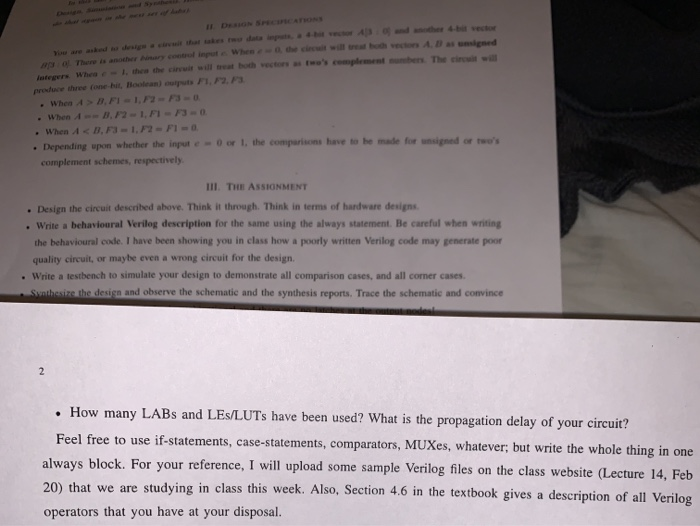

I. LABORATORY OBJECTIVES The purpose of this short, 1-week lab is to give you some practice with designing como give you some practice with designing combinational circuits using always @ statements in Verilog. So far, you have learnt how to design combinational logic using 5 ver primitives or using continuous assign statements. Now you are asked to use only always blocks to design combinational logic. In this lab, you will design and implement a configurable comparator using Verilog. You will performans Design, Simulation and Synthesis. However, there is no need to map and download the circuit onto FPGAs (well do that again in the next set of labs). II. DESIGN SPECIFICATIONS You are asked to design a circuit that takes two data inputs, a 4-bit vector A[3 : 0) and another 4-bit vector B[3:0). There is another binary control input c. When c = 0. the circuit will treat both vectors A, B as unsigned integers. When c = 1, then the circuit will treat both vectors as two's complement numbers. The circuit will produce three (one-bit, Boolean) outputs F1, F2, F3. . When A > B, F1 = 1, F2 = F3 = 0. . When A == B, F2 = 1, F1 = F3 = 0. . When A B, F1 = 1, F2 = F3 = 0. . When A == B, F2 = 1, F1 = F3 = 0. . When A

I. LABORATORY OBJECTIVES The purpose of this short, 1-week lab is to give you some practice with designing como give you some practice with designing combinational circuits using always @ statements in Verilog. So far, you have learnt how to design combinational logic using 5 ver primitives or using continuous assign statements. Now you are asked to use only always blocks to design combinational logic. In this lab, you will design and implement a configurable comparator using Verilog. You will performans Design, Simulation and Synthesis. However, there is no need to map and download the circuit onto FPGAs (well do that again in the next set of labs). II. DESIGN SPECIFICATIONS You are asked to design a circuit that takes two data inputs, a 4-bit vector A[3 : 0) and another 4-bit vector B[3:0). There is another binary control input c. When c = 0. the circuit will treat both vectors A, B as unsigned integers. When c = 1, then the circuit will treat both vectors as two's complement numbers. The circuit will produce three (one-bit, Boolean) outputs F1, F2, F3. . When A > B, F1 = 1, F2 = F3 = 0. . When A == B, F2 = 1, F1 = F3 = 0. . When A B, F1 = 1, F2 = F3 = 0. . When A == B, F2 = 1, F1 = F3 = 0. . When A

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started