Question

i need help with my quartas verilog code : ENTITY Tb_Carry_Look_Ahead IS END ENTITY Tb_Carry_Look_Ahead; ARCHITECTURE behavior OF Tb_Carry_Look_Ahead IS COMPONENT Carry_Look_Ahead PORT ( A

i need help with my quartas verilog code :

ENTITY Tb_Carry_Look_Ahead IS

END ENTITY Tb_Carry_Look_Ahead;

ARCHITECTURE behavior OF Tb_Carry_Look_Ahead IS

COMPONENT Carry_Look_Ahead

PORT (

A : IN std_logic_vector(3 downto 0);

B : IN std_logic_vector(3 downto 0);

Cin : IN std_logic;

S : OUT std_logic_vector(3 downto 0);

Cout : OUT std_logic

);

END COMPONENT;

signal A : std_logic_vector(3 downto 0) := (others => '0');

signal B : std_logic_vector(3 downto 0) := (others => '0');

signal Cin : std_logic := '0';

signal S : std_logic_vector(3 downto 0);

signal Cout : std_logic;

BEGIN

uut: Carry_Look_Ahead PORT MAP (

A => A,

B => B,

Cin => Cin,

S => S,

Cout => Cout

);

stim_proc: process

begin

-- Hold reset state for 100 ns.

wait for 100 ns;

A B Cin wait for 100 ns;

A B Cin wait for 100 ns;

A B Cin wait;

end process;

END ARCHITECTURE behavior;

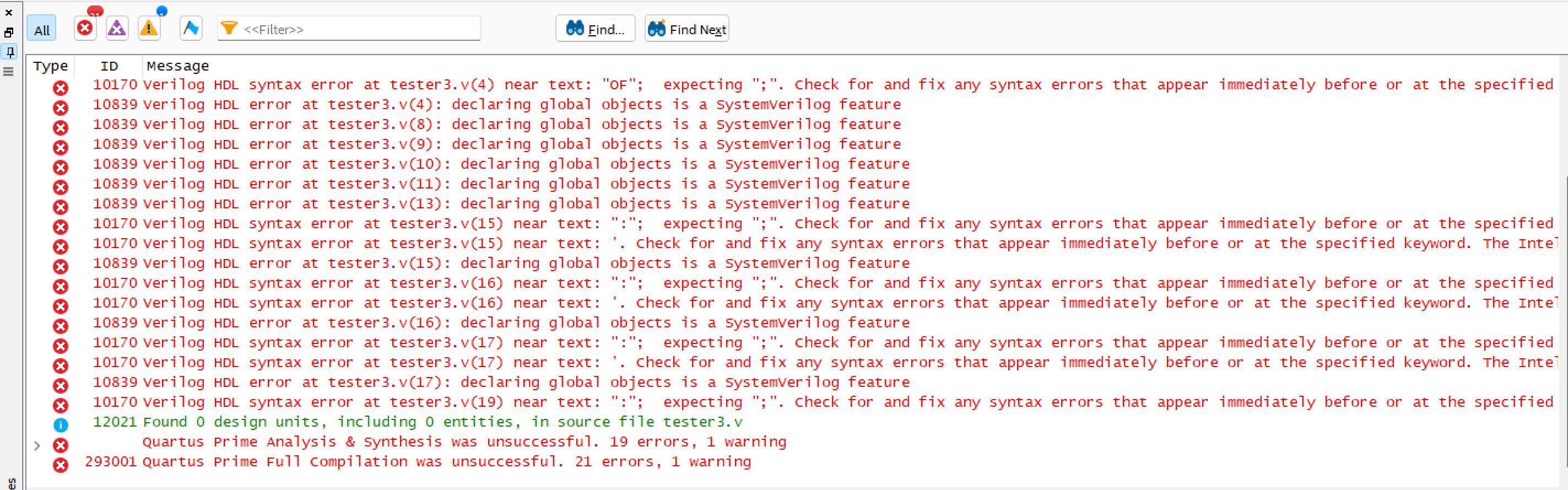

XIII 90 All ****** < > ************** Find... Type ID Message 10170 Verilog HDL syntax error at tester3.v(4) near text: "OF"; expecting ";". check for and fix any syntax errors that appear immediately before or at the specified 10839 verilog HDL error at tester 3. v(4): declaring global objects is a systemveri log feature error at tester 3. v(8): declaring global objects is a Systemveril og feature error at tester 3.v(9): declaring global objects is a Systemverilog feature error at tester 3. v(10): declaring global objects is a systemveril og feature error at tester 3.v(11): declaring global objects is a Systemverilog feature error at tester 3. v(13): declaring global objects is a systemverilog feature 10839 verilog HDL 10839 verilog HDL 10839 verilog HDL 10839 verilog HDL 10839 verilog HDL 10170 Verilog HDL 10170 verilog HDL 10839 verilog HDL 10170 verilog HDL syntax error at tester 3. v(16) near text: ""; expecting "; ". check for and fix any syntax errors that appear immediately before or at the specified 10170 Verilog HDL syntax error at tester 3. v(16) near text: '. check for and fix any syntax errors that appear immediately before or at the specified keyword. The Intel 10839 verilog HDL error at tester 3.v(16): declaring global objects is a Systemverilog feature 10170 verilog HDL syntax error at tester 3. v(17) near text: ":"; expecting "; ". check for and fix any syntax errors that appear immediately before or at the specified 10170 verilog HDL syntax error at tester 3. v(17) near text: '. check for and fix any syntax errors that appear immediately before or at the specified keyword. The Intel 10839 verilog HDL error at tester 3. v(17): declaring global objects is a Systemveril og feature 10170 verilog HDL syntax error at tester 3. v(19) near text: ":"; expecting "; ". check for and fix any syntax errors that appear immediately before or at the specified 12021 Found 0 design units, including 0 entities, in source file tester 3. v Quartus Prime Analysis & synthesis was unsuccessful. 19 errors, 1 warning 293001 Quartus Prime Full Compilation was unsuccessful. 21 errors, 1 warning Find Next syntax error at tester 3. v(15) near text: ""; expecting "; ". check for and fix any syntax errors that appear immediately before or at the specified syntax error at tester 3. v(15) near text: '. check for and fix any syntax errors that appear immediately before or at the specified keyword. The Intel error at tester 3. v(15): declaring global objects is a systemveril og feature

Step by Step Solution

3.41 Rating (154 Votes )

There are 3 Steps involved in it

Step: 1

The errors youre encountering in your Quartus Verilog code appear to be related to the language version and syntax used in the code The error message ...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started