Answered step by step

Verified Expert Solution

Question

1 Approved Answer

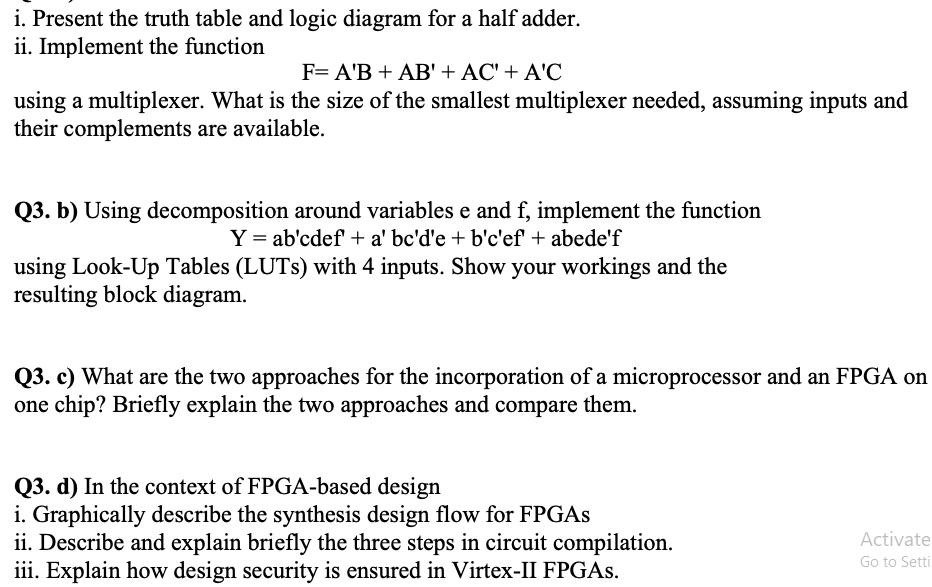

i. Present the truth table and logic diagram for a half adder. ii. Implement the function F= A'B + AB' + AC' + A'C

i. Present the truth table and logic diagram for a half adder. ii. Implement the function F= A'B + AB' + AC' + A'C using a multiplexer. What is the size of the smallest multiplexer needed, assuming inputs and their complements are available. Q3. b) Using decomposition around variables e and f, implement the function Y = ab'cdef + a' bc'd'e + b'c'ef + abede'f using Look-Up Tables (LUTs) with 4 inputs. Show your workings and the resulting block diagram. Q3. c) What are the two approaches for the incorporation of a microprocessor and an FPGA on one chip? Briefly explain the two approaches and compare them. Q3. d) In the context of FPGA-based design i. Graphically describe the synthesis design flow for FPGAs ii. Describe and explain briefly the three steps in circuit compilation. iii. Explain how design security is ensured in Virtex-II FPGAs. Activate Go to Setti

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started