Answered step by step

Verified Expert Solution

Question

1 Approved Answer

In a CMOS process, the value of the mobility correction factory is 2.8, while the parasitic delay of the inverter is Pin = =

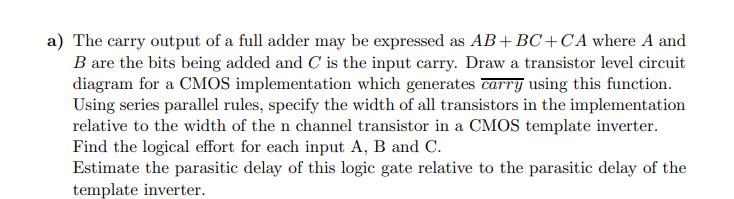

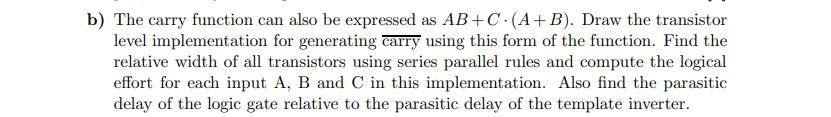

In a CMOS process, the value of the mobility correction factory is 2.8, while the parasitic delay of the inverter is Pin = = 2.4. a) The carry output of a full adder may be expressed as AB+BC+CA where A and B are the bits being added and C is the input carry. Draw a transistor level circuit diagram for a CMOS implementation which generates carry using this function. Using series parallel rules, specify the width of all transistors in the implementation relative to the width of the n channel transistor in a CMOS template inverter. Find the logical effort for each input A, B and C. Estimate the parasitic delay of this logic gate relative to the parasitic delay of the template inverter. b) The carry function can also be expressed as AB+C (A+B). Draw the transistor level implementation for generating carry using this form of the function. Find the relative width of all transistors using series parallel rules and compute the logical effort for each input A, B and C in this implementation. Also find the parasitic delay of the logic gate relative to the parasitic delay of the template inverter.

Step by Step Solution

★★★★★

3.52 Rating (159 Votes )

There are 3 Steps involved in it

Step: 1

The detailed ...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started