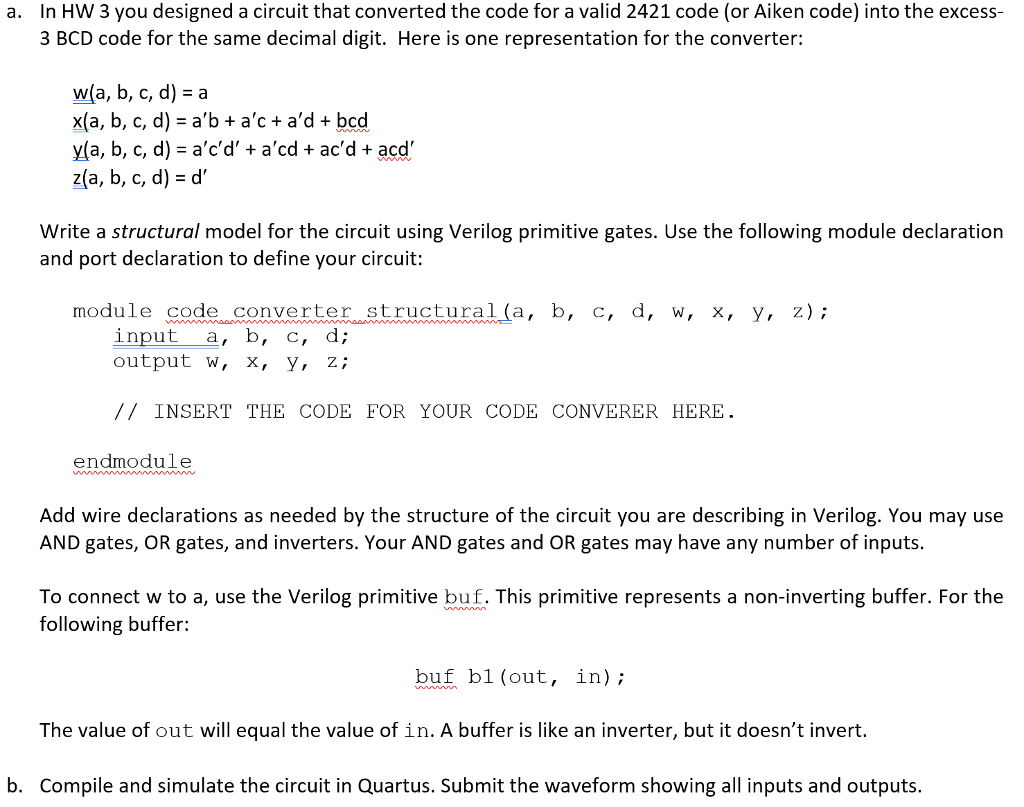

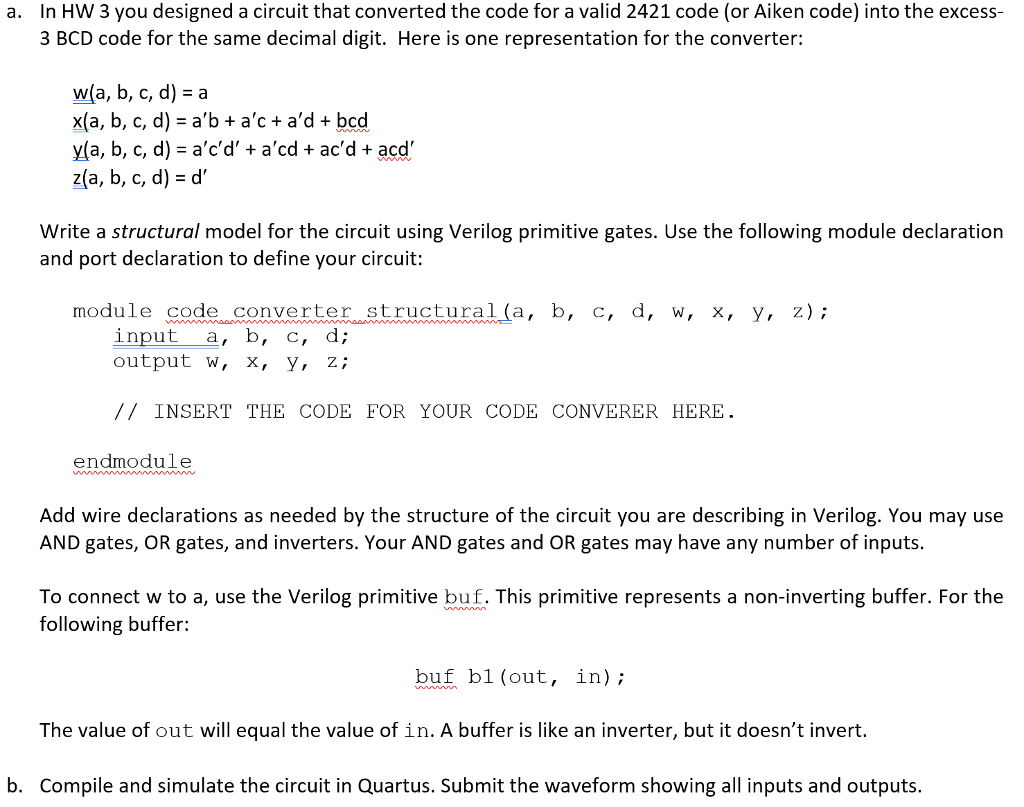

In HW 3 you designed a circuit that converted the code for a valid 2421 code (or Aiken code) into the excess- 3 BCD code for the same decimal digit. Here is one representation for the converter: a. (a, b, c, d) = a x(a, b, c, d) - a'b + a'c+ a'dbcd yla, b, c, d) - a'c'd' + a'cd+ ac'd acd' Z(a, b, c, d)- d' Write a structural model for the circuit using Verilog primitive gates. Use the following module declaration and port declaration to define your circuit: module code converter structural (a, b, c, d, w, x, y, z); input a, b, c, d; output W, x, y, z; // INSERT THE CODE FOR YOUR CODE CONVERER HERE endmodule Add wire declarations as needed by the structure of the circuit you are describing in Verilog. You may use AND gates, OR gates, and inverters. Your AND gates and OR gates may have any number of inputs. To connect w to a, use the Verilog primitive buf. This primitive represents a non-inverting buffer. For the following buffer: buf bl (out, in) The value of out will equal the value of in. A buffer is like an inverter, but it doesn't invert. b. Compile and simulate the circuit in Quartus. Submit the waveform showing all inputs and outputs. In HW 3 you designed a circuit that converted the code for a valid 2421 code (or Aiken code) into the excess- 3 BCD code for the same decimal digit. Here is one representation for the converter: a. (a, b, c, d) = a x(a, b, c, d) - a'b + a'c+ a'dbcd yla, b, c, d) - a'c'd' + a'cd+ ac'd acd' Z(a, b, c, d)- d' Write a structural model for the circuit using Verilog primitive gates. Use the following module declaration and port declaration to define your circuit: module code converter structural (a, b, c, d, w, x, y, z); input a, b, c, d; output W, x, y, z; // INSERT THE CODE FOR YOUR CODE CONVERER HERE endmodule Add wire declarations as needed by the structure of the circuit you are describing in Verilog. You may use AND gates, OR gates, and inverters. Your AND gates and OR gates may have any number of inputs. To connect w to a, use the Verilog primitive buf. This primitive represents a non-inverting buffer. For the following buffer: buf bl (out, in) The value of out will equal the value of in. A buffer is like an inverter, but it doesn't invert. b. Compile and simulate the circuit in Quartus. Submit the waveform showing all inputs and outputs