In this assignment, you will use the Design Compiler to accomplish the logic synthesis of the benchmark circuits obtained from ISCAS89 and perform pre-layout timing analysis using PrimeTime. There are 5 benchmark circuits of varying sizes. Perform the logic synthesis at two different frequencies: 100MHz and 500MHz.

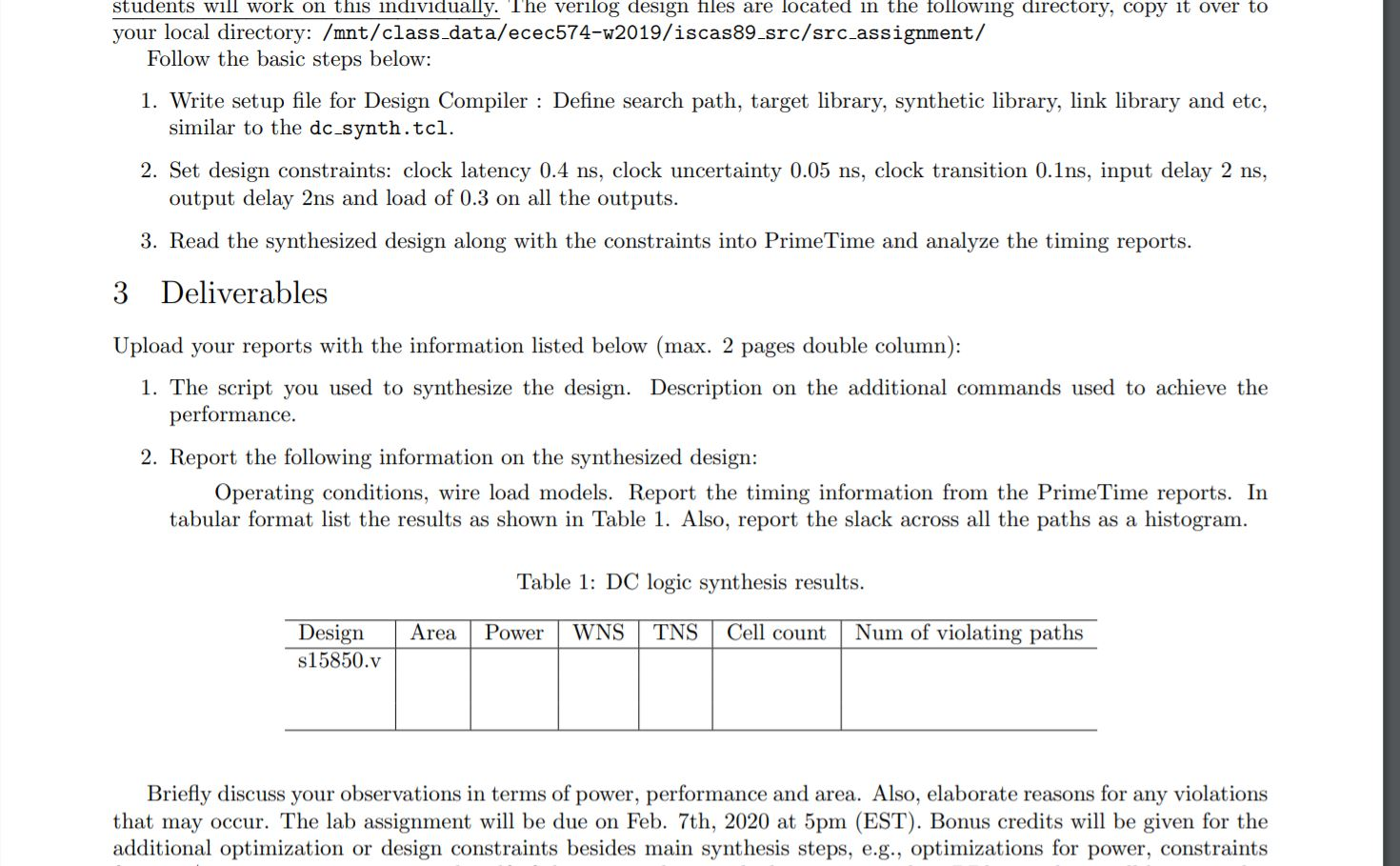

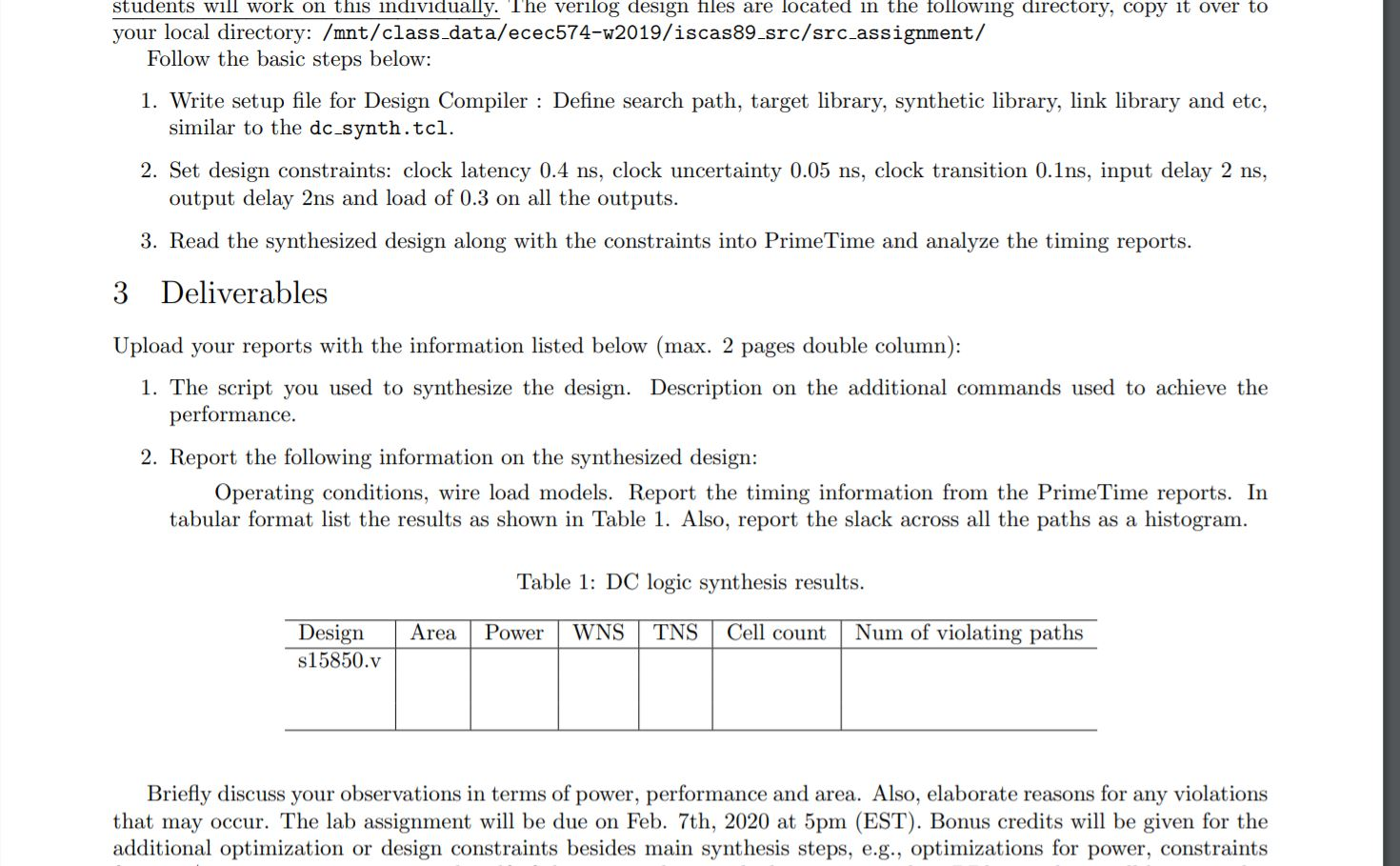

students will work on this individually. The verilog design files are located in the following directory, copy it over to your local directory: /mnt/class_data/ecec574-w2019/iscas89_src/src-assignment/ Follow the basic steps below: 1. Write setup file for Design Compiler : Define search path, target library, synthetic library, link library and etc, similar to the dc synth.tcl. 2. Set design constraints: clock latency 0.4 ns, clock uncertainty 0.05 ns, clock transition 0.1ns, input delay 2 ns, output delay 2ns and load of 0.3 on all the outputs. 3. Read the synthesized design along with the constraints into Prime Time and analyze the timing reports. 3 Deliverables Upload your reports with the information listed below (max. 2 pages double column): 1. The script you used to synthesize the design. Description on the additional commands used to achieve the performance. 2. Report the following information on the synthesized design: Operating conditions, wire load models. Report the timing information from the Prime Time reports. In tabular format list the results as shown in Table 1. Also, report the slack across all the paths as a histogram. Table 1: DC logic synthesis results. Area Power WNS TNS Cell count Num of violating paths Design s15850.v Briefly discuss your observations in terms of power, performance and area. Also, elaborate reasons for any violations that may occur. The lab assignment will be due on Feb. 7th, 2020 at 5pm (EST). Bonus credits will be given for the additional optimization or design constraints besides main synthesis steps, e.g., optimizations for power, constraints students will work on this individually. The verilog design files are located in the following directory, copy it over to your local directory: /mnt/class_data/ecec574-w2019/iscas89_src/src-assignment/ Follow the basic steps below: 1. Write setup file for Design Compiler : Define search path, target library, synthetic library, link library and etc, similar to the dc synth.tcl. 2. Set design constraints: clock latency 0.4 ns, clock uncertainty 0.05 ns, clock transition 0.1ns, input delay 2 ns, output delay 2ns and load of 0.3 on all the outputs. 3. Read the synthesized design along with the constraints into Prime Time and analyze the timing reports. 3 Deliverables Upload your reports with the information listed below (max. 2 pages double column): 1. The script you used to synthesize the design. Description on the additional commands used to achieve the performance. 2. Report the following information on the synthesized design: Operating conditions, wire load models. Report the timing information from the Prime Time reports. In tabular format list the results as shown in Table 1. Also, report the slack across all the paths as a histogram. Table 1: DC logic synthesis results. Area Power WNS TNS Cell count Num of violating paths Design s15850.v Briefly discuss your observations in terms of power, performance and area. Also, elaborate reasons for any violations that may occur. The lab assignment will be due on Feb. 7th, 2020 at 5pm (EST). Bonus credits will be given for the additional optimization or design constraints besides main synthesis steps, e.g., optimizations for power, constraints