Answered step by step

Verified Expert Solution

Question

1 Approved Answer

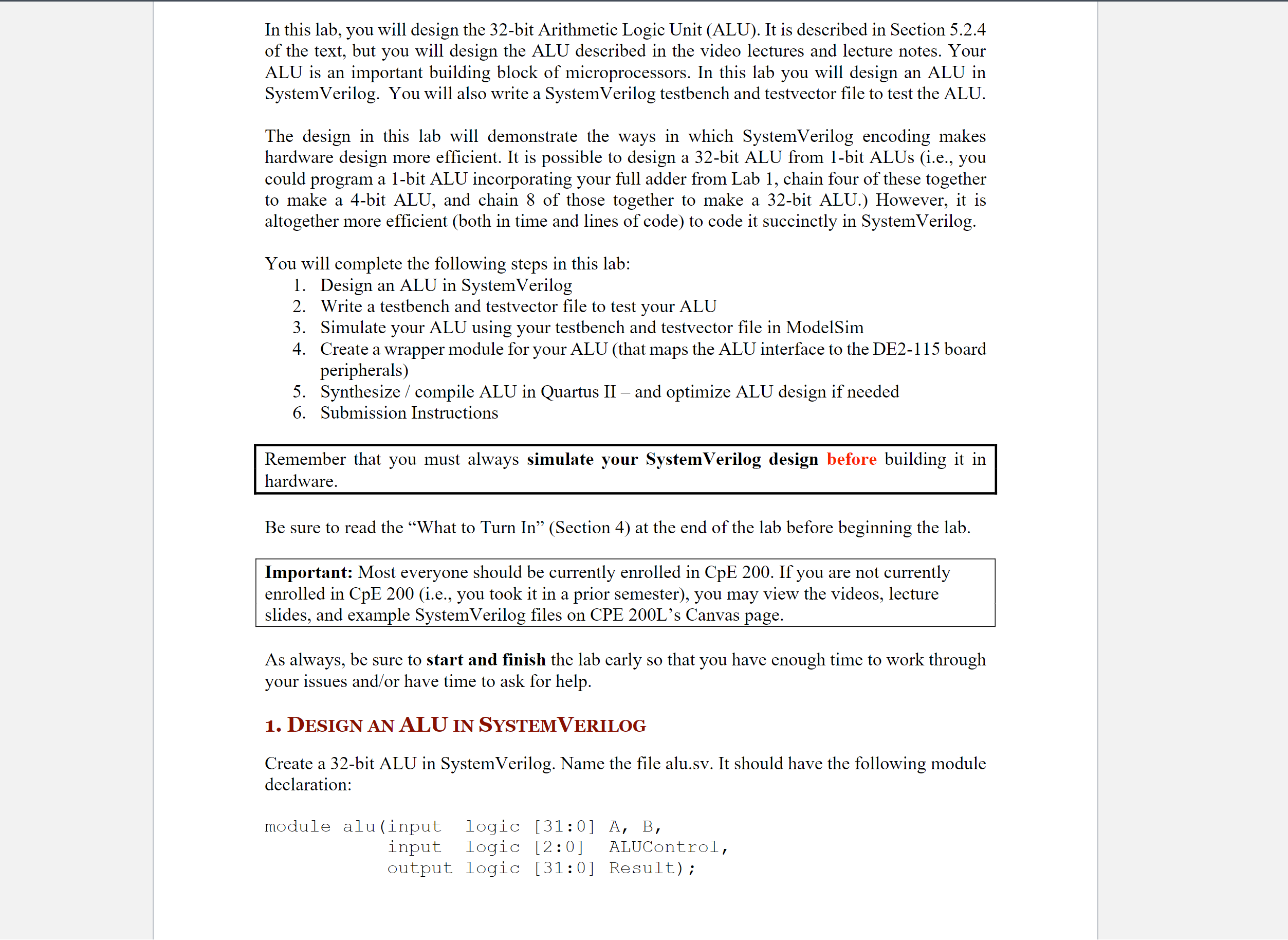

In this lab, you will design the 3 2 - bit Arithmetic Logic Unit ( ALU ) . It is described in Section 5 .

In this lab, you will design the bit Arithmetic Logic Unit ALU It is described in Section

of the text, but you will design the ALU described in the video lectures and lecture notes. Your

ALU is an important building block of microprocessors. In this lab you will design an ALU in

SystemVerilog. You will also write a SystemVerilog testbench and testvector file to test the ALU.

The design in this lab will demonstrate the ways in which SystemVerilog encoding makes

hardware design more efficient. It is possible to design a bit ALU from bit ALUs ie you

could program a bit ALU incorporating your full adder from Lab chain four of these together

to make a bit ALU, and chain of those together to make a bit ALU. However, it is

altogether more efficient both in time and lines of code to code it succinctly in SystemVerilog.

You will complete the following steps in this lab:

Design an ALU in SystemVerilog

Write a testbench and testvector file to test your ALU

Simulate your ALU using your testbench and testvector file in ModelSim

Create a wrapper module for your ALU that maps the ALU interface to the DE board

peripherals

Synthesize compile ALU in Quartus II and optimize ALU design if needed

Submission Instructions

Remember that you must always simulate your SystemVerilog design before building it in

hardware.

Be sure to read the "What to Turn InSection at the end of the lab before beginning the lab.

Important: Most everyone should be currently enrolled in CpE If you are not currently

enrolled in CpE ie you took it in a prior semester you may view the videos, lecture

slides, and example SystemVerilog files on CPE Ls Canvas page.

As always, be sure to start and finish the lab early so that you have enough time to work through

your issues andor have time to ask for help.

DESign AN ALU IN SYStEMVERILOG

Create a bit ALU in SystemVerilog. Name the file

alu.sv It should have the following module

declaration:

module aluinput logic : A B

input logic : ALUControl,

output logic : Result;

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started