Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Just question 2 Problem: Implement an ALU (Arithmetic Logic Unit) satisfying the following functional requirements. You should complete schematic capture tutorial, before you start on

Just question 2

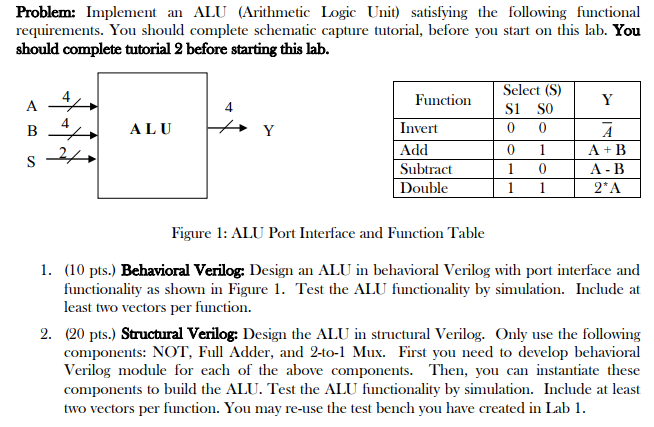

Problem: Implement an ALU (Arithmetic Logic Unit) satisfying the following functional requirements. You should complete schematic capture tutorial, before you start on this lab. You should complete tutorial 2 before starting this lab. A 4 Function ALU Y Select (S) si SO 1 0 0 101 A+B A -B 1 1 2A s Invert Add Subtract Double -2 Figure 1: ALU Port Interface and Function Table 1. (10 pts.) Behavioral Verilog: Design an ALU in behavioral Verilog with port interface and functionality as shown in Figure 1. Test the ALU functionality by simulation. Include at least two vectors per function. 2. (20 pts.) Structural Verilog: Design the ALU in structural Verilog. Only use the following components: NOT, Full Adder, and 2-to-1 Mux. First you need to develop behavioral Verilog module for each of the above components. Then, you can instantiate these components to build the ALU. Test the ALU functionality by simulation. Include at least two vectors per function. You may re-use the test bench you have created in Lab 1. Problem: Implement an ALU (Arithmetic Logic Unit) satisfying the following functional requirements. You should complete schematic capture tutorial, before you start on this lab. You should complete tutorial 2 before starting this lab. A 4 Function ALU Y Select (S) si SO 1 0 0 101 A+B A -B 1 1 2A s Invert Add Subtract Double -2 Figure 1: ALU Port Interface and Function Table 1. (10 pts.) Behavioral Verilog: Design an ALU in behavioral Verilog with port interface and functionality as shown in Figure 1. Test the ALU functionality by simulation. Include at least two vectors per function. 2. (20 pts.) Structural Verilog: Design the ALU in structural Verilog. Only use the following components: NOT, Full Adder, and 2-to-1 Mux. First you need to develop behavioral Verilog module for each of the above components. Then, you can instantiate these components to build the ALU. Test the ALU functionality by simulation. Include at least two vectors per function. You may re-use the test bench you have created in Lab 1Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started