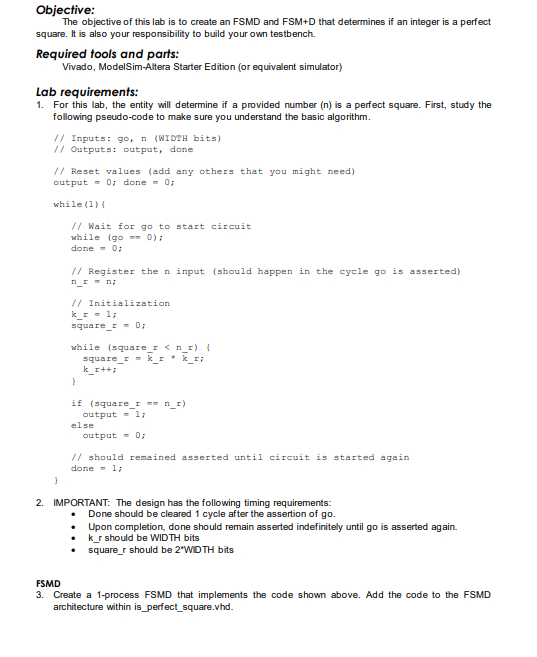

Question: library ieee; use ieee.std _ logic _ 1 1 6 4 . all; use ieee.numeric _ std . all; entity fsm is generic ( WIDTH

library ieee;

use ieee.stdlogicall;

use ieee.numericstdall;

entity fsm is

generic

WIDTH : positive :;

port

clk : in stdlogic;

rst : in stdlogic;

go : in stdlogic;

done : out stdlogic;

nen : out stdlogic;

outputen : out stdlogic;

ken : out stdlogic;

ksel : out stdlogic;

squareen : out stdlogic;

squaresel : out stdlogic;

squareltn : in stdlogic;

end fsm;

architecture defaultarch of fsm is

begin defaultarch

end defaultarch; FOR fsmvhd

library ieee;

use ieee.stdlogicall;

use ieee.numericstdall;

entity datapath is

generic

WIDTH : positive

;

port

clk : in stdlogic;

rst : in stdlogic;

n : in stdlogicvectorWIDTH downto ;

output : out stdlogic;

nen : in stdlogic;

outputen : in stdlogic;

ken : in stdlogic;

ksel : in stdlogic;

squareen : in stdlogic;

squaresel : in stdlogic;

squareltn : out stdlogic

;

end datapath;

architecture defaultarch of datapath is

begin

end defaultarch;for datapath.vhd

library ieee;

use ieee.stdlogicall;

use ieee.numericstdall;

entity isperfectsquare is

generic

WIDTH : positive :;

port

clk : in stdlogic;

rst : in stdlogic;

go : in stdlogic;

done : out stdlogic;

n : in stdlogicvectorWIDTH downto ;

output : out stdlogic;

end isperfectsquare;

architecture FSMD of isperfectsquare is

begin FSMD

end FSMD;

architecture FSMD of isperfectsquare is

begin

end architecture FSMD;

architecture defaultarch of isperfectsquare is

begin

NOTE: Change the architecture here to synthesizesimulate each implementation.

TOP : entity work.isperfectsquareFSMD

generic map

WIDTH WIDTH

port map

clk clk

rst rst

go go

done done,

n n

output output

;

end defaultarch;

for isperfectsquare.vhd

library ieee;

use ieee.stdlogicall;

use ieee.numericstdall;

use ieee.mathreal.all;

entity isperfectsquaretb is

end isperfectsquaretb;

architecture defaulttb of isperfectsquaretb is

begin

end defaulttb;

for isperfectsquaretb vhd

Step by Step Solution

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock