Question

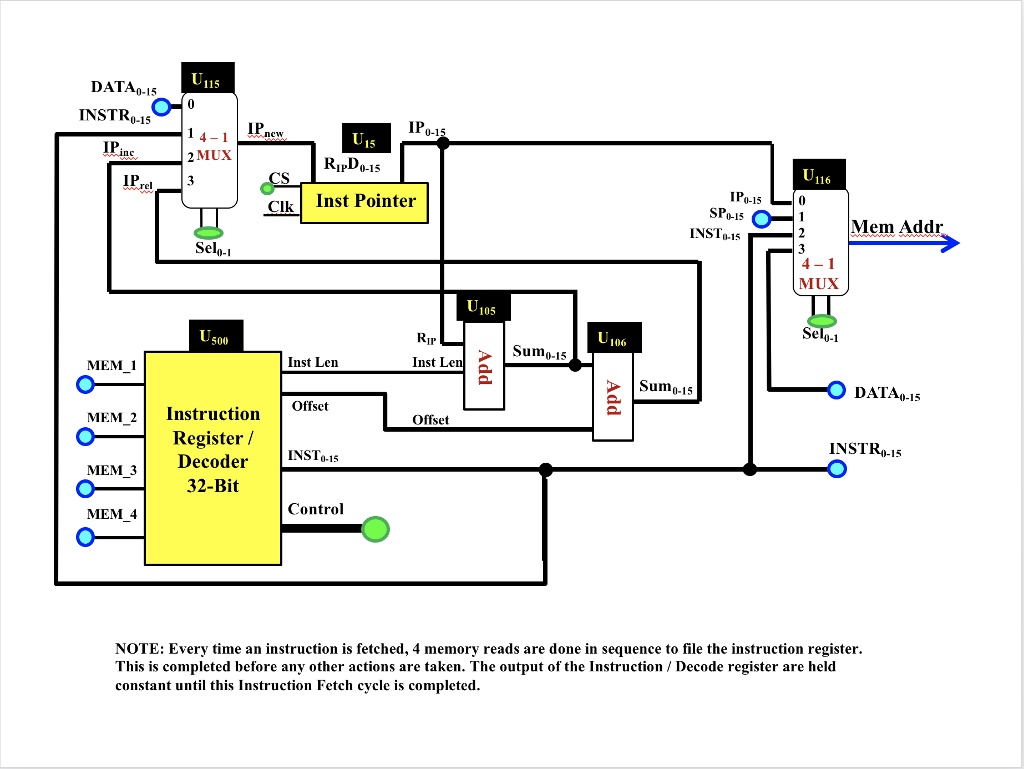

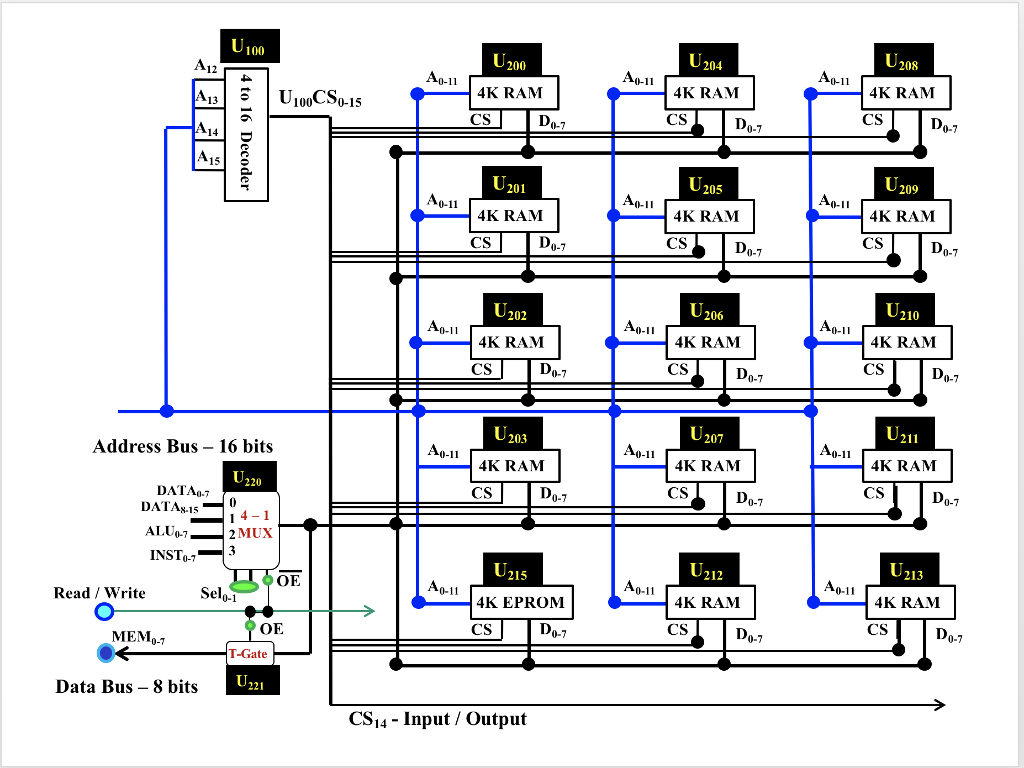

Please I need help with the following questions! 1. Describe how the Mov R23, $12CD instruction would work on the following architecture. This instruction moves

Please I need help with the following questions!

1. Describe how the "Mov R23, $12CD" instruction would work on the following architecture. This instruction moves the value hex 12CD into register 2 and register 3 with register 2 being the most significant byte.

2. Describe the hardware required to implement the Addc R1,[$FC12,R2] instruction. This instruction adds the value $FC12 to the contents of register to resulting in a memory address. The value at that address is read and added to the contents of register 1 along with the current value of the carry flag. The result is stored in register 1. This instruction may require several clock cycles depending on how you implement it as well as several pieces of hardware. Implement it however you like. Any hardware you add should start with U600 to preclude using a number already used.

3. Briefly describe how the xor R0,R1 would work on using the architecture.

4. Briefly describe what hardware/inputs/outputs would need to be added to implement the following instruction: xor R3,$35. Exclusive-or the value $35 with the contents of register 3 and store the result in register 3.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started