Answered step by step

Verified Expert Solution

Question

1 Approved Answer

PLEASE INCLUDE ACTUAL CIRCUIT CODE, ACTUAL TEST BENCH CODE AND WAVEFORM IMAGE, BY ACTUAL I MEAN DO NOT USE HANDWRITTEN FOR SYNTAX PURPOSES Problem 3:

PLEASE INCLUDE ACTUAL CIRCUIT CODE, ACTUAL TEST BENCH CODE AND WAVEFORM IMAGE, BY ACTUAL I MEAN DO NOT USE HANDWRITTEN FOR SYNTAX PURPOSES

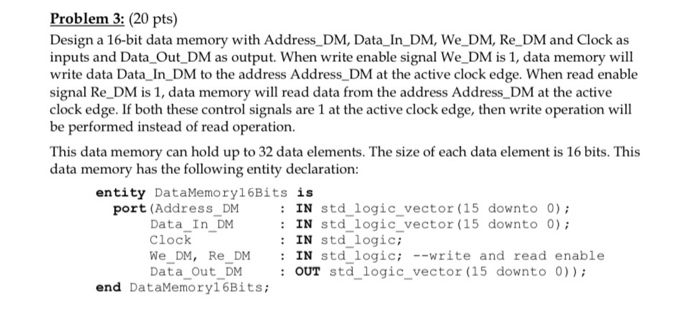

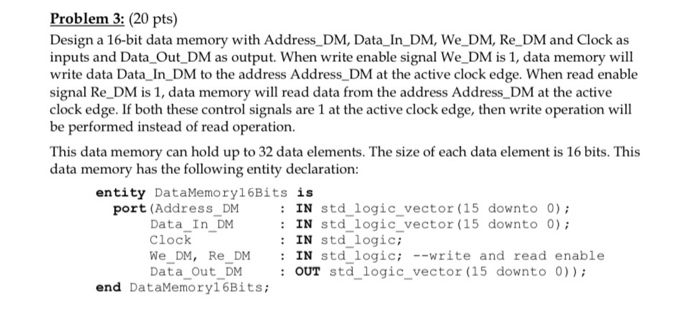

Problem 3: (20 pts) Design a 16-bit data memory with Address_DM, Data_In_DM, We_DM, Re_DM and Clock as inputs and Data Out_DM as output. When write enable signal We_DM is 1, data memory will write data Data In DM to the address Address_DM at the active clock edge. When read enable signal Re DM is 1, data memory will read data from the address AddressDM at the active clock edge. If both these control signals are 1 at the active clock edge, then write operation will be performed instead of read operation This data memory can hold up to 32 data elements. The size of each data element is 16 bits. This data memory has the following entity declaration: entity DataMemory16Bits is port (Address_DM I N std_logic_vector (15 downto 0); Data_In_DM I N std_logic_vector (15 downto 0); Clock : IN std logic; We_DM, Re_DM I N std_logic; --write and read enable Data_out_DM : OUT std_logic_vector (15 downto 0)); end DataMemory16Bits; Problem 3: (20 pts) Design a 16-bit data memory with Address_DM, Data_In_DM, We_DM, Re_DM and Clock as inputs and Data Out_DM as output. When write enable signal We_DM is 1, data memory will write data Data In DM to the address Address_DM at the active clock edge. When read enable signal Re DM is 1, data memory will read data from the address AddressDM at the active clock edge. If both these control signals are 1 at the active clock edge, then write operation will be performed instead of read operation This data memory can hold up to 32 data elements. The size of each data element is 16 bits. This data memory has the following entity declaration: entity DataMemory16Bits is port (Address_DM I N std_logic_vector (15 downto 0); Data_In_DM I N std_logic_vector (15 downto 0); Clock : IN std logic; We_DM, Re_DM I N std_logic; --write and read enable Data_out_DM : OUT std_logic_vector (15 downto 0)); end DataMemory16Bits

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started