Answered step by step

Verified Expert Solution

Question

1 Approved Answer

please solve with steps . Questions 72 - 75 are based on the following information: A pipelined processor has the following features: Four pipeline stages:

please solve with steps

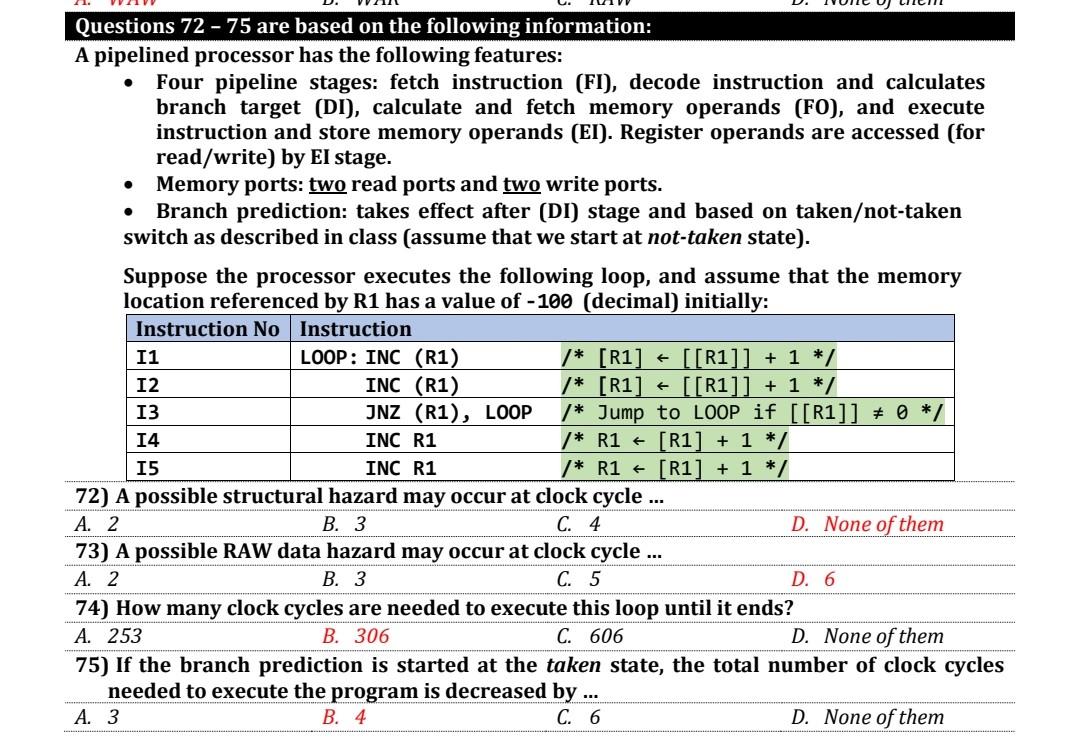

. Questions 72 - 75 are based on the following information: A pipelined processor has the following features: Four pipeline stages: fetch instruction (FI), decode instruction and calculates branch target (DI), calculate and fetch memory operands (FO), and execute instruction and store memory operands (EI). Register operands are accessed (for read/write) by EI stage. Memory ports: two read ports and two write ports. Branch prediction: takes effect after (DI) stage and based on takenot-taken switch as described in class (assume that we start at not-taken state). Suppose the processor executes the following loop, and assume that the memory location referenced by R1 has a value of -100 (decimal) initially: Instruction No Instruction 11 LOOP: INC (R1) /* [R1] [[R1]] + 1 */ 12 INC (R1) /* [R1] [[R1]] + 1 */ 13 JNZ (R1), LOOP /* Jump to LOOP if [[R1]] # 0 */ 14 INC R1 /* R1 + [R1] + 1 */ 15 INC R1 /* R1 + [R1] + 1 */ 72) A possible structural hazard may occur at clock cycle A. 2 B. 3 C. 4 D. None of them 73) A possible RAW data hazard may occur at clock cycle ... A. 2 B. 3 C. 5 D. 6 74) How many clock cycles are needed to execute this loop until it ends? A. 253 B. 306 C.606 D. None of them 75) If the branch prediction is started at the taken state, the total number of clock cycles needed to execute the program is decreased by ... A. 3 B. 4 C. 6 D. None of themStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started