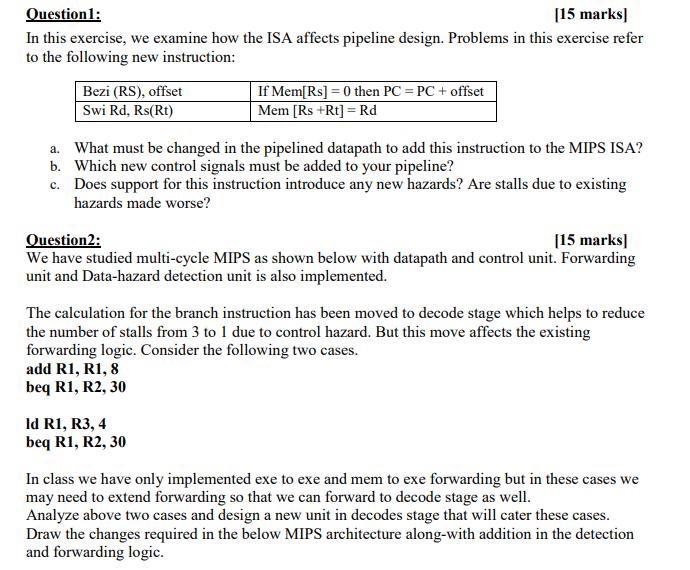

Question1: [15 marks) In this exercise, we examine how the ISA affects pipeline design. Problems in this exercise refer to the following new instruction: Bezi (RS), offset If Mem[Rs] =0 then PC = PC + offset Swi Rd, Rs(Rt) Mem [Rs +Rt] = Rd a. What must be changed in the pipelined datapath to add this instruction to the MIPS ISA? b. Which new control signals must be added to your pipeline? c. Does support for this instruction introduce any new hazards? Are stalls due to existing hazards made worse? Question2: [15 marks We have studied multi-cycle MIPS as shown below with datapath and control unit. Forwarding unit and Data-hazard detection unit is also implemented. The calculation for the branch instruction has been moved to decode stage which helps to reduce the number of stalls from 3 to 1 due to control hazard. But this move affects the existing forwarding logic. Consider the following two cases. add R1, R1, 8 beq R1, R2, 30 ld R1, R3, 4 beq R1, R2, 30 In class we have only implemented exe to exe and mem to exe forwarding but in these cases we may need to extend forwarding so that we can forward to decode stage as well. Analyze above two cases and design a new unit in decodes stage that will cater these cases. Draw the changes required in the below MIPS architecture along with addition in the detection and forwarding logic. Question1: [15 marks) In this exercise, we examine how the ISA affects pipeline design. Problems in this exercise refer to the following new instruction: Bezi (RS), offset If Mem[Rs] =0 then PC = PC + offset Swi Rd, Rs(Rt) Mem [Rs +Rt] = Rd a. What must be changed in the pipelined datapath to add this instruction to the MIPS ISA? b. Which new control signals must be added to your pipeline? c. Does support for this instruction introduce any new hazards? Are stalls due to existing hazards made worse? Question2: [15 marks We have studied multi-cycle MIPS as shown below with datapath and control unit. Forwarding unit and Data-hazard detection unit is also implemented. The calculation for the branch instruction has been moved to decode stage which helps to reduce the number of stalls from 3 to 1 due to control hazard. But this move affects the existing forwarding logic. Consider the following two cases. add R1, R1, 8 beq R1, R2, 30 ld R1, R3, 4 beq R1, R2, 30 In class we have only implemented exe to exe and mem to exe forwarding but in these cases we may need to extend forwarding so that we can forward to decode stage as well. Analyze above two cases and design a new unit in decodes stage that will cater these cases. Draw the changes required in the below MIPS architecture along with addition in the detection and forwarding logic