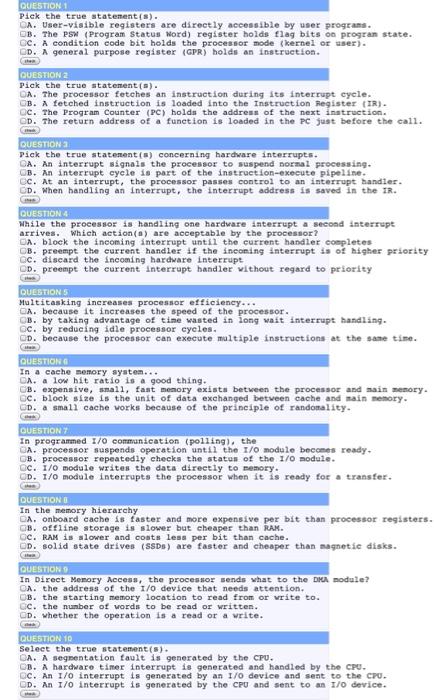

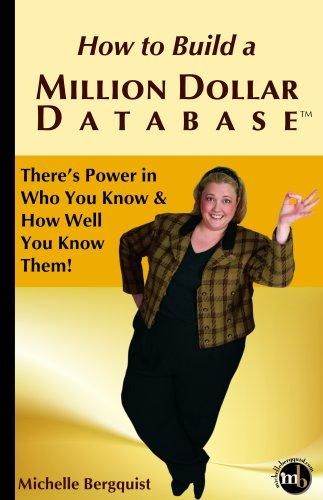

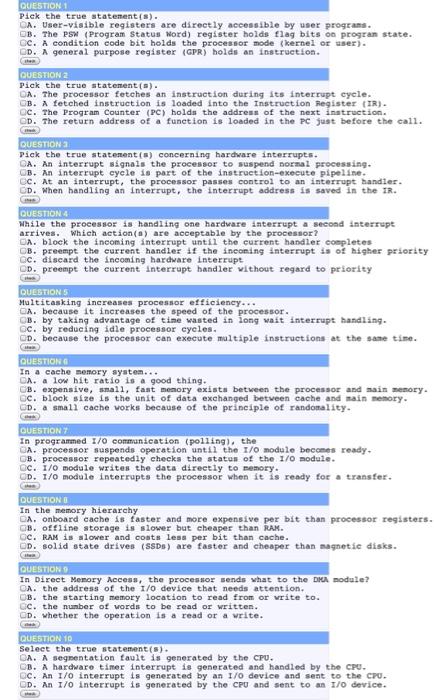

select the options that are true

there is more than one true answer

QUESTION 1 Pick the true statement(s). OA. User-visible registers are directly accessible by user programs. B. The PSW (Program Status word) register holds flag bits on program state. oc. A condition code bit holds the processor mode (kernel or user). OD. A general purpose register (GPR) holds an instruction. QUESTION 2 Pick the true statement(a). OA. The processor fetches an instruction during its interrupt cycle. OB. A fetched instruction is loaded into the Instruction Register (IR). Oc. The Program Counter (PC) holds the address of the next instruction. OD. The return address of a function is loaded in the PC just before the call. QUESTIONS Pick the true statement(s) concerning hardware interrupts. CA. An interrupt signals the processor to suspend normal processing. OB. An interrupt cycle is part of the instruction-execute pipeline. ec. At an interrupt, the processor passes control to an interrupt handler. OD. When handling an interrupt, the interrupt address is saved in the IR. QUESTION 4 While the processor is handling one hardware interrupt a second interrupt arrives. Which action(s) are acceptable by the processor? CA. block the incoming interrupt until the current handler completes B. preempt the current handler if the incoming interrupt is of higher priority OC. discard the incoming hardware interrupt D. preempt the current interrupt handler vithout regard to priority QUESTIONS Multitasking increases processor efficiency... OA. because it increases the speed of the processor B. by taking advantage of time wasted in long wait interrupt handling. D. because the processor can execute multiple instructions at the same time. QUESTIONS In a cache memory system... DA. a low hit ratio is a good thing. CB. expensive, small, fast memory exists between the processor and sain memory. cc. block size is the unit of data exchanged between cache and main memory. D. a small cache works because of the principle of randomality. QUESTION In programmed I/O communication (polling), the A. processor suspends operation until the I/O module becomes ready. OB. processor repeatedly checks the status of the 1/0 module. c. 1/0 module writes the data directly to memory. OD. 1/0 module interrupts the processor when it is ready for a transfer. QUESTION O In the memory hierarchy DA onboard cache is faster and more expensive per bit than processor registers. GB. offline storage is slower but cheaper than RAM. OC. RAM is slower and costs less per bit than cache. OD. solid state drives (SSDs) are faster and cheaper than magnetic disks. QUESTIONS In Direct Memory Access, the processor sends what to the DNA sodule? On the address of the I/O device that needs attention. OB. the starting memory location to read from or write to. cc. the number of words to be read or written. OD. Whether the operation is a read or a write. QUESTION 10 Select the true statement(s). DA. A segmentation fault is generated by the CPU. OB. A hardware timer interrupt is generated and handled by the cpu. OC. An I/O interrupt is generated by an 1/0 device and sent to the CPU. ED. An 170 interrupt is generated by the CPU and sent to an 1/0 device