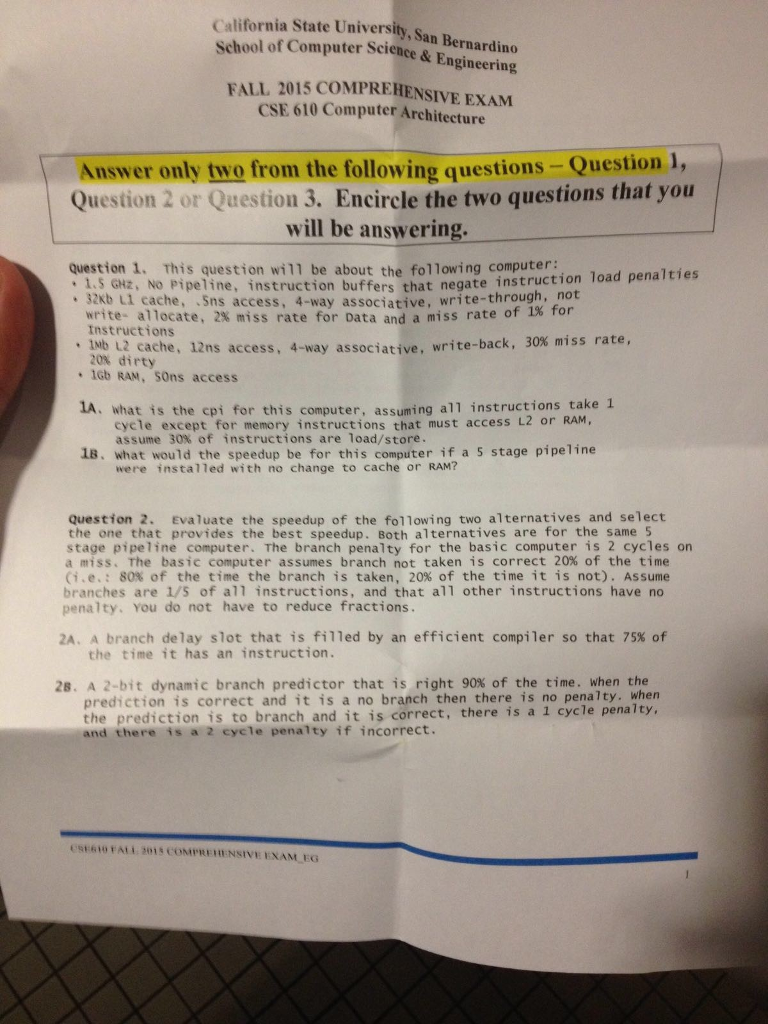

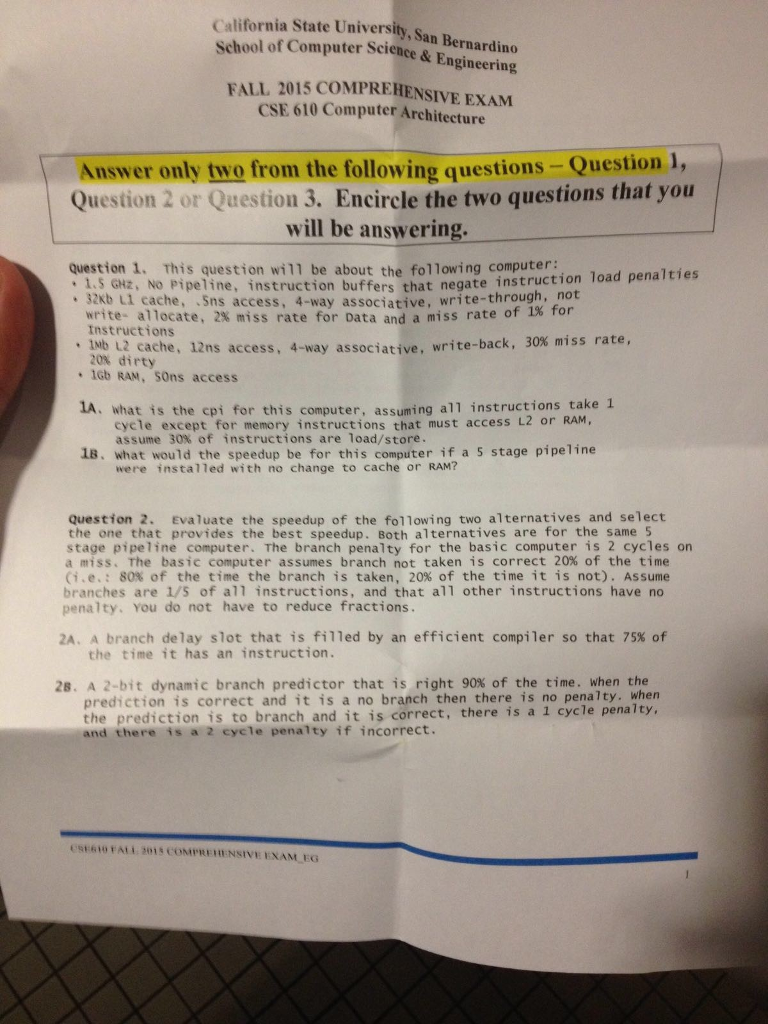

State Univers school of ty, s Computer Science an & Engineering FALL 2015 COMPREHENSIVE ExAM CSE 610 Computer Architecture Answer only two from the following questions- Question 1 Question 2 or Question 3. Encircle the two questions that you will be answering. Question 1. This question will be about the following computer load penalties 1 GHz. No Pipeline, instruction buffers that 32Kb L1 cache, .5ns access, 4-way associative, write-through, not write allocate, 2x miss rate for Data and a miss rate of 1% Instructions Mb L2 cache, 12ns 4-way associative, write-back, 30% miss rate, access, 1 20x dirty 1Gb RAM, sons access IA. what is the cpi for this computer, assuming all instructions take 1 cycle except for memory instructions that must access L2 or RAM, assume 30% of instructions are load/store. lB. what would the speedup be for this computer if a 5 stage pipeline were installed with no change to cache or RAM? Question 2 Evaluate the speedup of the following two alternatives and select the one that provides the best speedup. Both alternatives are for the same 5 stage pipeline computer. The branch penalty for the basic computer is 2 cycles on The basic computer assumes branch not taken is correct 20% of the time 80R of the time the branch is taken, 20% of the time it is not). Assume branches are 1/5 of all instructions, and that all other instructions have no penalty. You do not have to reduce fractions. anch delay slot that is filled by an efficient compiler so that 75% of the time it has an instruction branch predictor that is right 90% of the time. when the 2s. A prediction is correct and it is a no branch then there is no penalty. When the prediction is branch and it is correct, there is a cycle penalty, to is a 2 cycle penalty if incorrect and there est to EA ii 3015 COMPRE NSIVE ENAM EG State Univers school of ty, s Computer Science an & Engineering FALL 2015 COMPREHENSIVE ExAM CSE 610 Computer Architecture Answer only two from the following questions- Question 1 Question 2 or Question 3. Encircle the two questions that you will be answering. Question 1. This question will be about the following computer load penalties 1 GHz. No Pipeline, instruction buffers that 32Kb L1 cache, .5ns access, 4-way associative, write-through, not write allocate, 2x miss rate for Data and a miss rate of 1% Instructions Mb L2 cache, 12ns 4-way associative, write-back, 30% miss rate, access, 1 20x dirty 1Gb RAM, sons access IA. what is the cpi for this computer, assuming all instructions take 1 cycle except for memory instructions that must access L2 or RAM, assume 30% of instructions are load/store. lB. what would the speedup be for this computer if a 5 stage pipeline were installed with no change to cache or RAM? Question 2 Evaluate the speedup of the following two alternatives and select the one that provides the best speedup. Both alternatives are for the same 5 stage pipeline computer. The branch penalty for the basic computer is 2 cycles on The basic computer assumes branch not taken is correct 20% of the time 80R of the time the branch is taken, 20% of the time it is not). Assume branches are 1/5 of all instructions, and that all other instructions have no penalty. You do not have to reduce fractions. anch delay slot that is filled by an efficient compiler so that 75% of the time it has an instruction branch predictor that is right 90% of the time. when the 2s. A prediction is correct and it is a no branch then there is no penalty. When the prediction is branch and it is correct, there is a cycle penalty, to is a 2 cycle penalty if incorrect and there est to EA ii 3015 COMPRE NSIVE ENAM EG