Question: The ARM assembly program shown below right runs in a system with a five-stage pipelined instructio execution unit and a memory latency of three

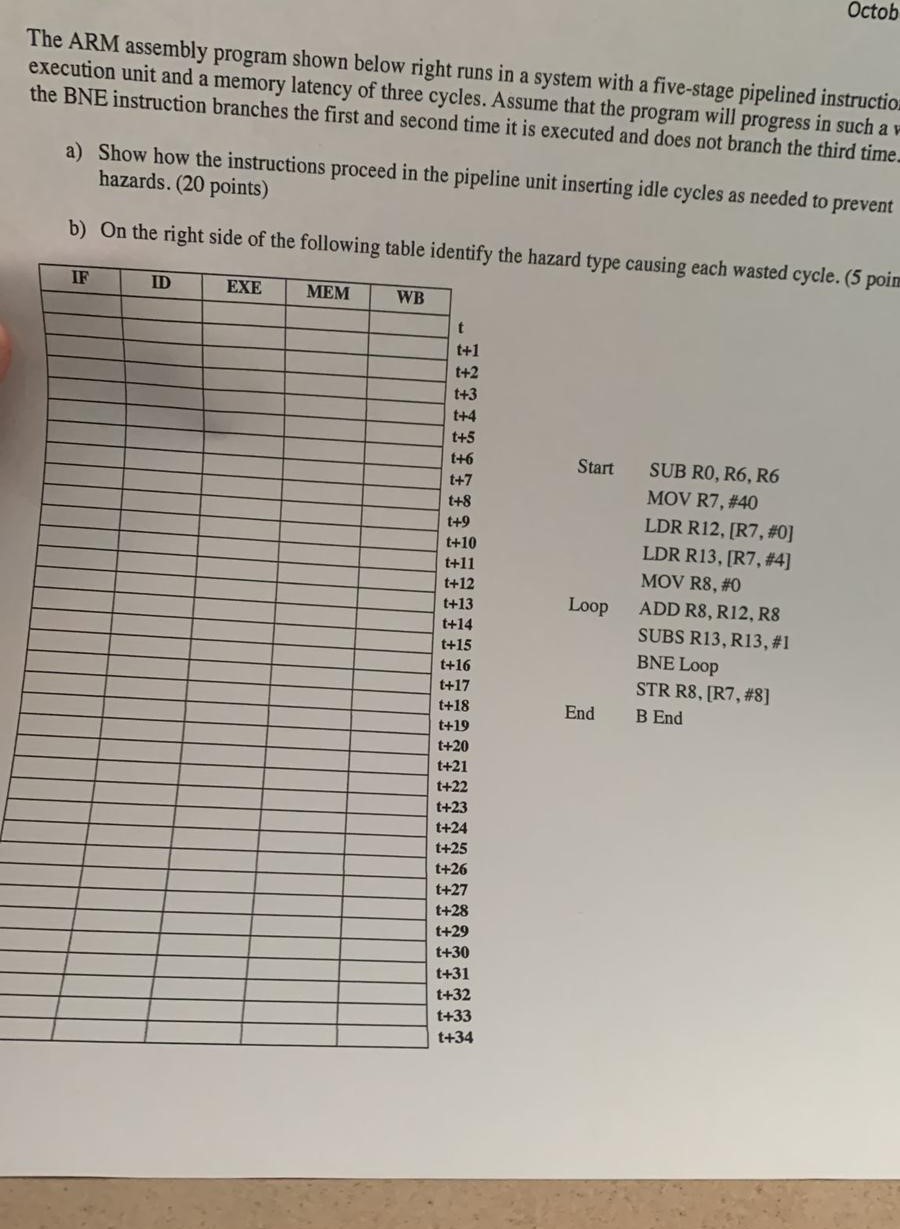

The ARM assembly program shown below right runs in a system with a five-stage pipelined instructio execution unit and a memory latency of three cycles. Assume that the program will progress in such a v the BNE instruction branches the first and second time it is executed and does not branch the third time. a) Show how the instructions proceed in the pipeline unit inserting idle cycles as needed to prevent hazards. (20 points) b) On the right side of the following table identify the hazard type causing each wasted cycle. (5 poin IF ID EXE MEM WB t t+1 t+2 t+3 t+4 t+5 t+6 t+7 t+8 t+9 t+10 t+11 t+12 t+13 t+14 t+15 t+16 t+17 t+18 t+19 t+20 t+21 t+22 t+23 t+24 t+25 t+26 t+27 t+28 t+29 t+30 t+31 t+32 t+33 t+34 Start Loop Octob End SUB R0, R6, R6 MOV R7, # 40 LDR R12, [R7 , #0] LDR R13, [R7, #4] MOV R8, #0 ADD R8, R12, R8 SUBS R13, R13 , #1 BNE Loop STR R8, [R7, #8] B End The ARM assembly program shown below right runs in a system with a five-stage pipelined instructio execution unit and a memory latency of three cycles. Assume that the program will progress in such a v the BNE instruction branches the first and second time it is executed and does not branch the third time. a) Show how the instructions proceed in the pipeline unit inserting idle cycles as needed to prevent hazards. (20 points) b) On the right side of the following table identify the hazard type causing each wasted cycle. (5 poin IF ID EXE MEM WB t t+1 t+2 t+3 t+4 t+5 t+6 t+7 t+8 t+9 t+10 t+11 t+12 t+13 t+14 t+15 t+16 t+17 t+18 t+19 t+20 t+21 t+22 t+23 t+24 t+25 t+26 t+27 t+28 t+29 t+30 t+31 t+32 t+33 t+34 Start Loop Octob End SUB R0, R6, R6 MOV R7, # 40 LDR R12, [R7 , #0] LDR R13, [R7, #4] MOV R8, #0 ADD R8, R12, R8 SUBS R13, R13 , #1 BNE Loop STR R8, [R7, #8] B End

Step by Step Solution

There are 3 Steps involved in it

The image shows a question about processing an ARM assembly program with a fivestage pipelined instruction execution unit IF Instruction Fetch ID Instruction Decode EXE Execute MEM Memory access WB Wr... View full answer

Get step-by-step solutions from verified subject matter experts