Answered step by step

Verified Expert Solution

Question

1 Approved Answer

The control signals and Datapath operations: wrt _ addr signal provides an address to activate the required register as stated in Table 1 . Table

The control signals and Datapath operations:

wrtaddr signal provides an address to activate the required register as stated in Table

Table : to Decoder Operation

wrten works together with the wrtaddr to select either a new value or hold the previous value.

ToggleTH also works with the wrten and wrtaddr to set either the Temperature setting or the

Humidity Setting.

loaddata signal selects either the new TemperatureHumidity UserSensor values from the to

MUX or the ALU output result for feedback.

Inputsel is used to select the UserTemperature, SensorTemperature, UserHumidity,

SensorHumidity. Note: we use a bit data path so these values should lie between

rdaddr and rdaddr signals provide the register addresses that are required to perform the CCU

operations between two registers using the ceuopeode provided. The CCU must be designed with the

following operations stated in Table You can use the behavioural approach to design the CCU.

Table : ALU Opcodes and Instructions.

Please note that these signals must be used in Datapath testbench to test all possible conditions required to

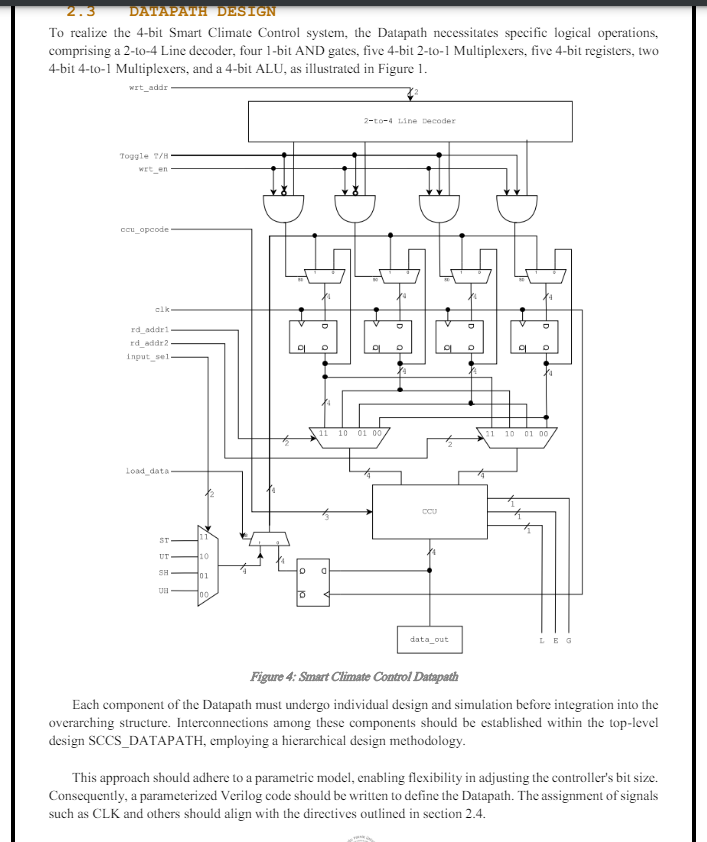

perform operations for SCCSTo realize the bit Smart Climate Control system, the Datapath necessitates specific logical operations,

comprising a to Line decoder, four bit AND gates, five bit to Multiplexers, five bit registers, two

bit to Multiplexers, and a bit ALU, as illustrated in Figure

Figure : Smart Climate Control Datapath

Each component of the Datapath must undergo individual design and simulation before integration into the

overarching structure. Interconnections among these components should be established within the toplevel

design SCCSDATAPATH, employing a hierarchical design methodology.

This approach should adhere to a parametric model, enabling flexibility in adjusting the controller's bit size.

Consequently, a parameterized Verilog code should be written to define the Datapath. The assignment of signals

such as CLK and others should align with the directives outlined in section

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started