Question

The first problem focuses on simplified results of the Xilinx XQR5VFX130 SRAM based FPGA summarized in: Allen, G., Edmonds, L., Tseng, C.W., Swift, G. and

The first problem focuses on simplified results of the Xilinx XQR5VFX130 SRAM based FPGA summarized in:

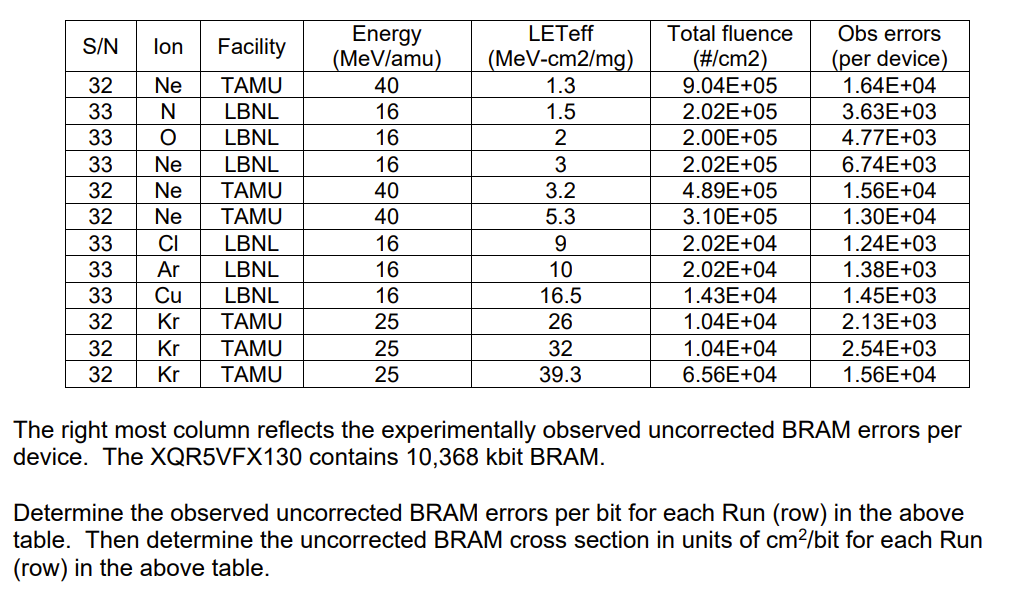

Allen, G., Edmonds, L., Tseng, C.W., Swift, G. and Carmichael, C. Single-Event Upset (SEU) Results of Embedded Error Detect and Correct Enabled Block Random Access Memory (Block RAM) Within the Xilinx XQR5VFX130. IEEE TNS Vol. 57, No. 6, December 2010, pp. 3426-3431.

It is not necessary (or required) that students acquire and read the paper to complete the homework assignment. Students are, of course, welcome to read and digest the entirety of the paper but we will focus on the data presented in Table II of the paper and reproduced here under.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started