Question

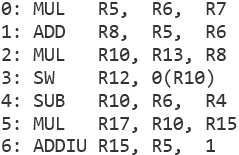

The following code is to be executed on a processor with 32 architectural registers. The processor is able to issue instructions out-of-order. The processor is

The following code is to be executed on a processor with 32 architectural registers. The processor is able to issue instructions out-of-order. The processor is a single issue machine. The processor has different functional unit latencies with multiply instructions having a latency of 4 cycles, ALU operations having a latency of 1 cycles, and loads and stores having a latency of 2 cycles. The processor stalls on WAW and WAR dependencies. Pretend that you are the compiler and perform changes to the following code to increase the performance of the code when executing on this out-of-order processor. Assume that all registers not used are free to be used by the compiler.

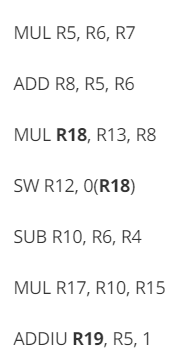

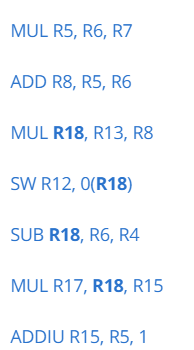

Which of the following code sequences would increase the performance of the code on this OoO processor? Select all that apply.

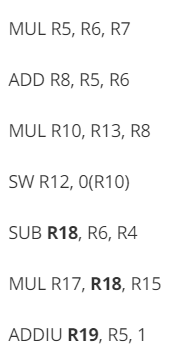

a)

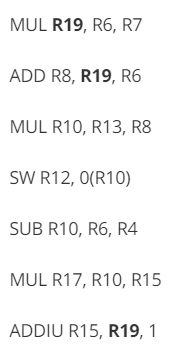

b)

c)

d)

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started