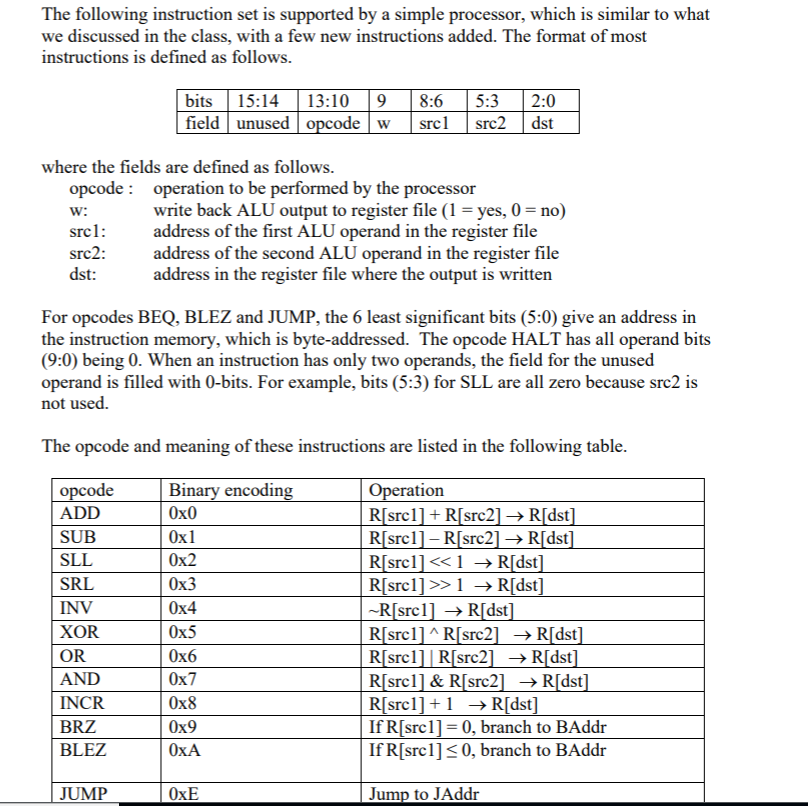

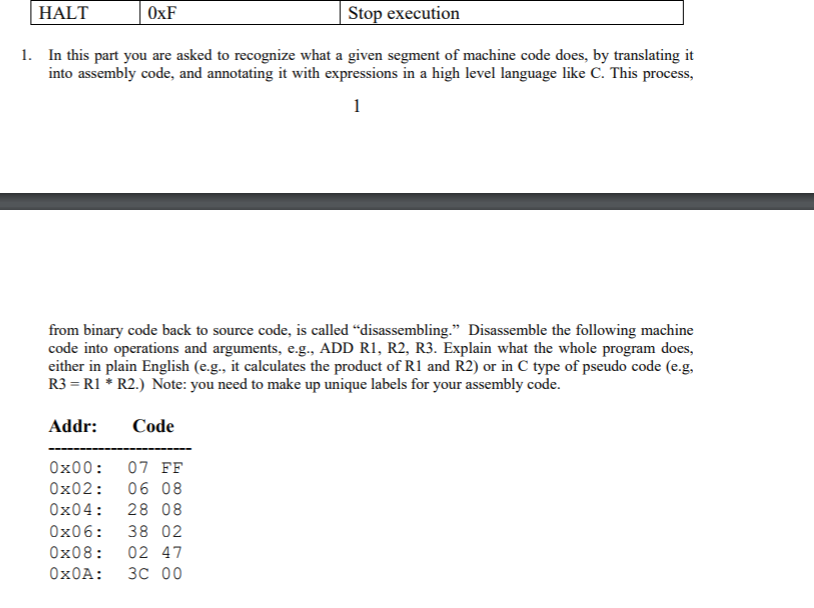

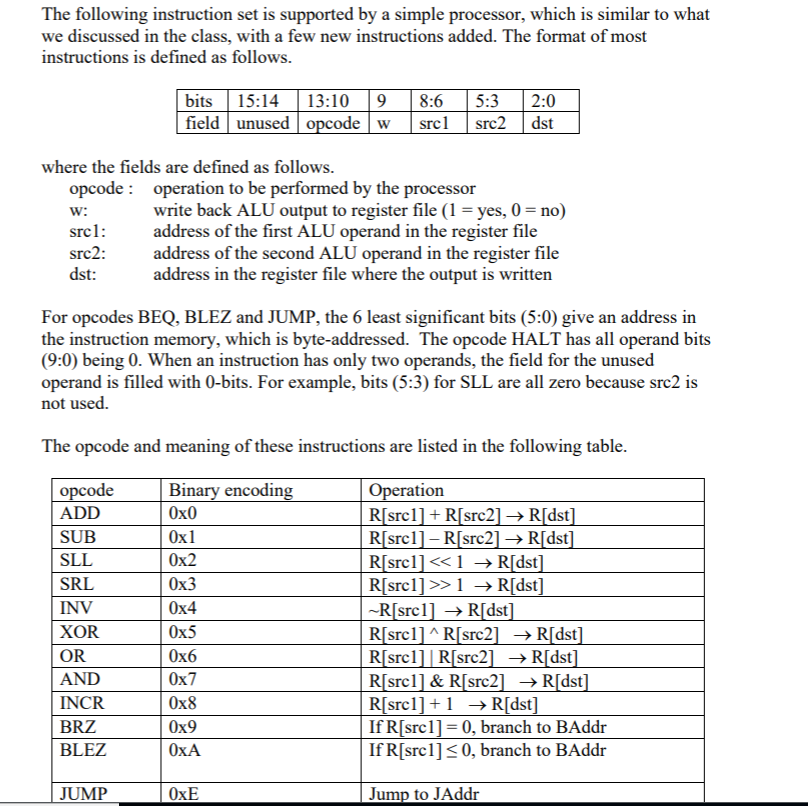

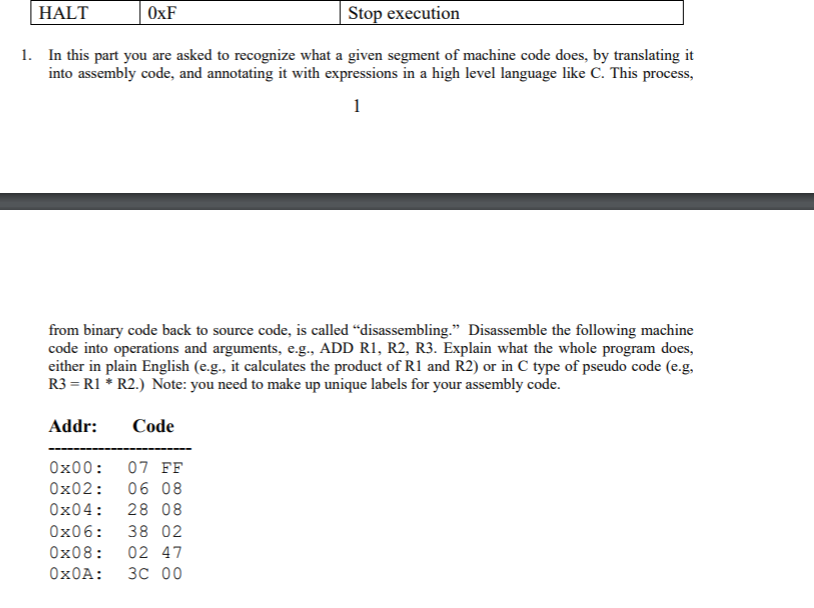

The following instruction set is supported by a simple processor, which is similar to what we discussed in the class, with a few new instructions added. The format of most instructions is defined as follows. bits 15:14 13:10 98:6 5:3 2:0 field unused opcode Src src2 dst where the fields are defined as follows. opcode: W: srcl src2 operation to be performed by the processor write back ALU output to register file (1 = yes, 0 = no) address of the first ALU operand in the register file address of the second ALU operand in the register file address in the register file where the output is written For opcodes BEQ, BLEZ and JUMP, the 6 least significant bits (5:0) give an address in the instruction memory, which is byte-addressed. The opcode HALT has all operand bits (9:0) being 0. When an instruction has only two operands, the field for the unused operand is filled with 0-bits. For example, bits (5:3) for SLL are all zero because src2 is not used. The opcode and meaning of these instructions are listed in the following table Binary encodin 0x0 ode ation ADD SUB SLL SRL INV XOR OR AND INCR BRZ BLEZ 0x2 0x3 0x4 0x5 0x6 0x7 0x8 0x9 0xA RIsrcI] > 1 Rldst src src21 RIdst RIsrc 11 & RIsrc21 R(dst IfRIsrc 11-0, branch to BAddr If R[srcl] 0, branch to BAddr JUMP 0xE Jump to JAddr The following instruction set is supported by a simple processor, which is similar to what we discussed in the class, with a few new instructions added. The format of most instructions is defined as follows. bits 15:14 13:10 98:6 5:3 2:0 field unused opcode Src src2 dst where the fields are defined as follows. opcode: W: srcl src2 operation to be performed by the processor write back ALU output to register file (1 = yes, 0 = no) address of the first ALU operand in the register file address of the second ALU operand in the register file address in the register file where the output is written For opcodes BEQ, BLEZ and JUMP, the 6 least significant bits (5:0) give an address in the instruction memory, which is byte-addressed. The opcode HALT has all operand bits (9:0) being 0. When an instruction has only two operands, the field for the unused operand is filled with 0-bits. For example, bits (5:3) for SLL are all zero because src2 is not used. The opcode and meaning of these instructions are listed in the following table Binary encodin 0x0 ode ation ADD SUB SLL SRL INV XOR OR AND INCR BRZ BLEZ 0x2 0x3 0x4 0x5 0x6 0x7 0x8 0x9 0xA RIsrcI] > 1 Rldst src src21 RIdst RIsrc 11 & RIsrc21 R(dst IfRIsrc 11-0, branch to BAddr If R[srcl] 0, branch to BAddr JUMP 0xE Jump to JAddr