Answered step by step

Verified Expert Solution

Question

1 Approved Answer

There is no more information which is given. Can you explain me which conditions do you need to solve this problem? Question 14) Consider an

There is no more information which is given. Can you explain me which conditions do you need to solve this problem?

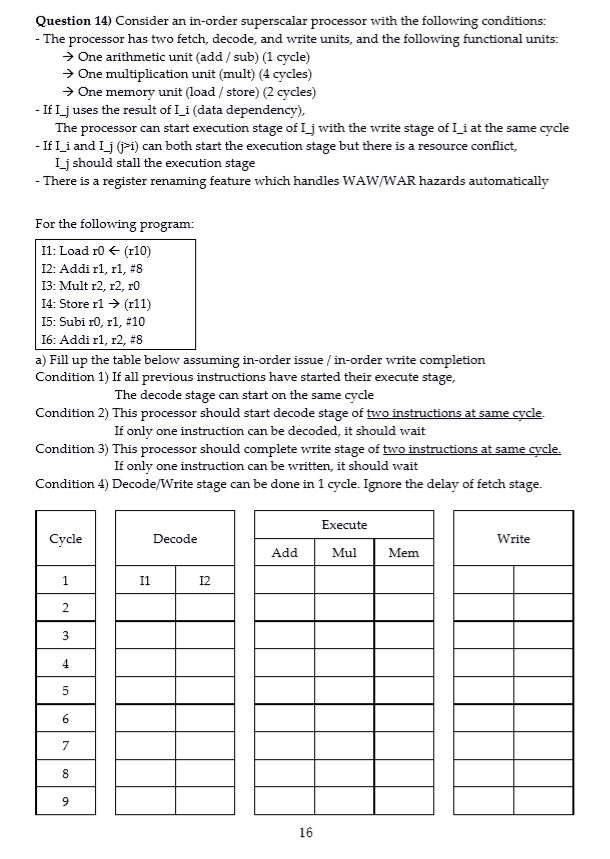

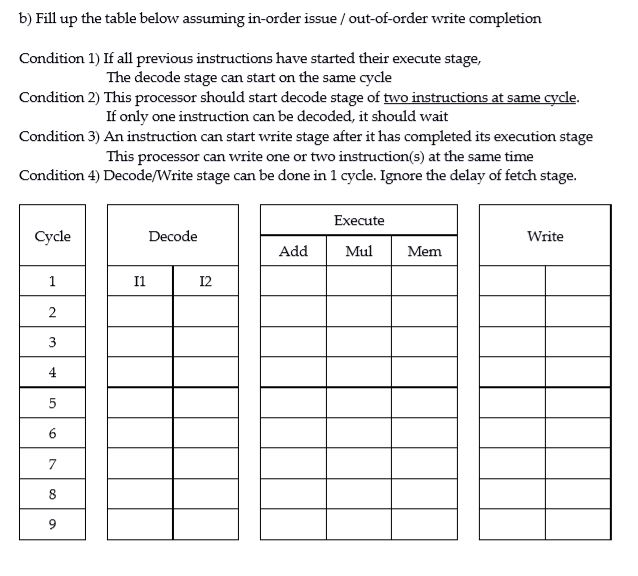

Question 14) Consider an in-order superscalar processor with the following conditions: - The processor has two fetch, decode, and write units, and the following functional units. One arithmetic unit (add / sub) (1 cycle) One multiplication unit (mult) (4 cycles) One memory unit (load /store) (2 cycles) - If I_j uses the result of I_i (data dependency), The processor can start execution stage of Ij with the write stage of I_i at the same cycle - If I i and I_j (Si) can both start the execution stage but there is a resource conflict, Ij should stall the execution stage - There is a register renaming feature which handles WAW/WAR hazards automatically For the following program: 11: Load ro (110) 12: Addi rl, r1, #8 13: Mult r2, r2, r0 14: Store rl (111) 15: Subi r0, 11, #10 16: Addi rl, r2, #8 a) Fill up the table below assuming in-order issue / in-order write completion Condition 1) If all previous instructions have started their execute stage, The decode stage can start on the same cycle Condition 2) This processor should start decode stage of two instructions at same cycle. If only one instruction can be decoded, it should wait Condition 3) This processor should complete write stage of two instructions at same cycle. If only one instruction can be written, it should wait Condition 4) Decode/Write stage can be done in 1 cycle. Ignore the delay of fetch stage. Execute Cycle Decode Write Add Mul Mem 1 11 12 2 3 4 UI 6 7 8 9 16 b) Fill up the table below assuming in-order issue / out-of-order write completion Condition 1) If all previous instructions have started their execute stage, The decode stage can start on the same cycle Condition 2) This processor should start decode stage of two instructions at same cycle. If only one instruction can be decoded, it should wait Condition 3) An instruction can start write stage after it has completed its execution stage This processor can write one or two instruction(s) at the same time Condition 4) Decode/Write stage can be done in 1 cycle. Ignore the delay of fetch stage. Execute Cycle Decode Write Add Mul Mem 1 11 12 2 4 5 6 7 8 ON Question 14) Consider an in-order superscalar processor with the following conditions: - The processor has two fetch, decode, and write units, and the following functional units. One arithmetic unit (add / sub) (1 cycle) One multiplication unit (mult) (4 cycles) One memory unit (load /store) (2 cycles) - If I_j uses the result of I_i (data dependency), The processor can start execution stage of Ij with the write stage of I_i at the same cycle - If I i and I_j (Si) can both start the execution stage but there is a resource conflict, Ij should stall the execution stage - There is a register renaming feature which handles WAW/WAR hazards automatically For the following program: 11: Load ro (110) 12: Addi rl, r1, #8 13: Mult r2, r2, r0 14: Store rl (111) 15: Subi r0, 11, #10 16: Addi rl, r2, #8 a) Fill up the table below assuming in-order issue / in-order write completion Condition 1) If all previous instructions have started their execute stage, The decode stage can start on the same cycle Condition 2) This processor should start decode stage of two instructions at same cycle. If only one instruction can be decoded, it should wait Condition 3) This processor should complete write stage of two instructions at same cycle. If only one instruction can be written, it should wait Condition 4) Decode/Write stage can be done in 1 cycle. Ignore the delay of fetch stage. Execute Cycle Decode Write Add Mul Mem 1 11 12 2 3 4 UI 6 7 8 9 16 b) Fill up the table below assuming in-order issue / out-of-order write completion Condition 1) If all previous instructions have started their execute stage, The decode stage can start on the same cycle Condition 2) This processor should start decode stage of two instructions at same cycle. If only one instruction can be decoded, it should wait Condition 3) An instruction can start write stage after it has completed its execution stage This processor can write one or two instruction(s) at the same time Condition 4) Decode/Write stage can be done in 1 cycle. Ignore the delay of fetch stage. Execute Cycle Decode Write Add Mul Mem 1 11 12 2 4 5 6 7 8 ONStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started