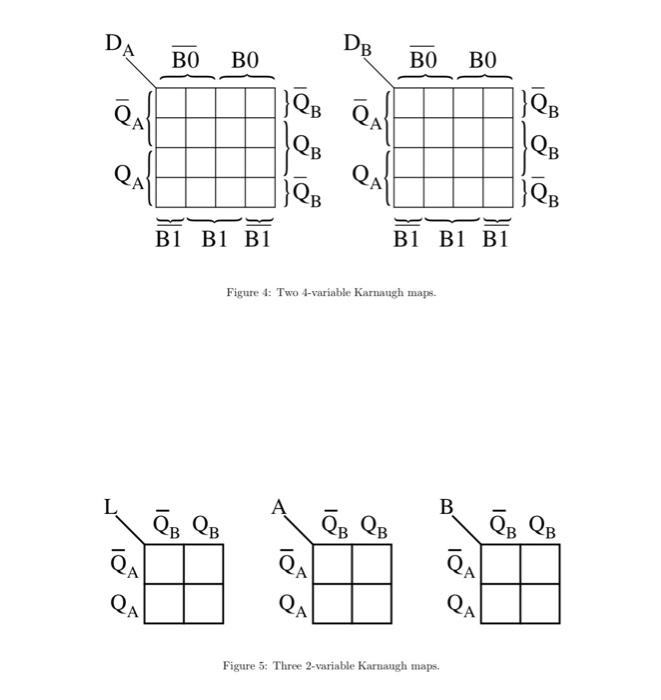

This problem requires you to design a discrete-logic circuit that realizes a Moore finite state machine (FSM)for implementing the cipher lock started in Problem Set 2. To receive credit you must base your design on the state diagram and state table provided in the solutions for Problem Set 2. In addition, you must use the notation for the states, inputs, and outputs defined in Problem Set 2. 1. (15 points) Using the state table provided in the solutions for Problem Set 2, and the four-variable Karnaugh maps shown in figure 4, determine the input equations for the two D-type flip-flop inputs DA and DB. To receive credit, your solution must use the variable assignments appearing in the provided Karnaugh map and cach minterm must be assigned as 0 or 1. No credit will be given if you alter the location of variables in the Karnaugh map provided. Also, use the state table provided in the solutions for Problem Set 2 and the two variable Karnaugh maps shown in figure 5 to determine the outputs in terms of QA and QB. 2. (15 points) Realize the finite state machine using the gates and flip-flop parts provided in your lab kit. You can't exceed the available gate count and input types provided in your kit! If you run out of one type of gate, you may need to substitute another. For example, if you run out of qund input nand gates: You could use an 8-input nand with four inputs tied high. You could assemble a 4-input nand using four 2-input nands. Assume that each D-type flip-flop has an asynchronous input labeled CLR that drives the flip-flop output to logie low whenever the value of CLR is logic high; these will serve as your reset input. Nently sketch your circuit. As an alternative to sketching, you can use Lab 3. Exercise 2 as an example to implement the logie diagram in Multisim; specifically, see the circuit implemented on page 19. You are just "sketching" (schematic capture) at this point so there is no need for the function generator to represent the clock. As part of your first project, you will use Multisim to simulate your FSM, so you will be able to use your Multisim sketch as the basis for your simulation DA DB BO BO BO BO QA QB A QB IQB IQB QN QN }QB }QB B1 B1 B1 B1 B1 B1 Figure 4: Two 4-variable Karnaugh maps. L B OB QB OB QB TA A QA Figure 5: Three 2-variable Karnaugh maps