Answered step by step

Verified Expert Solution

Question

1 Approved Answer

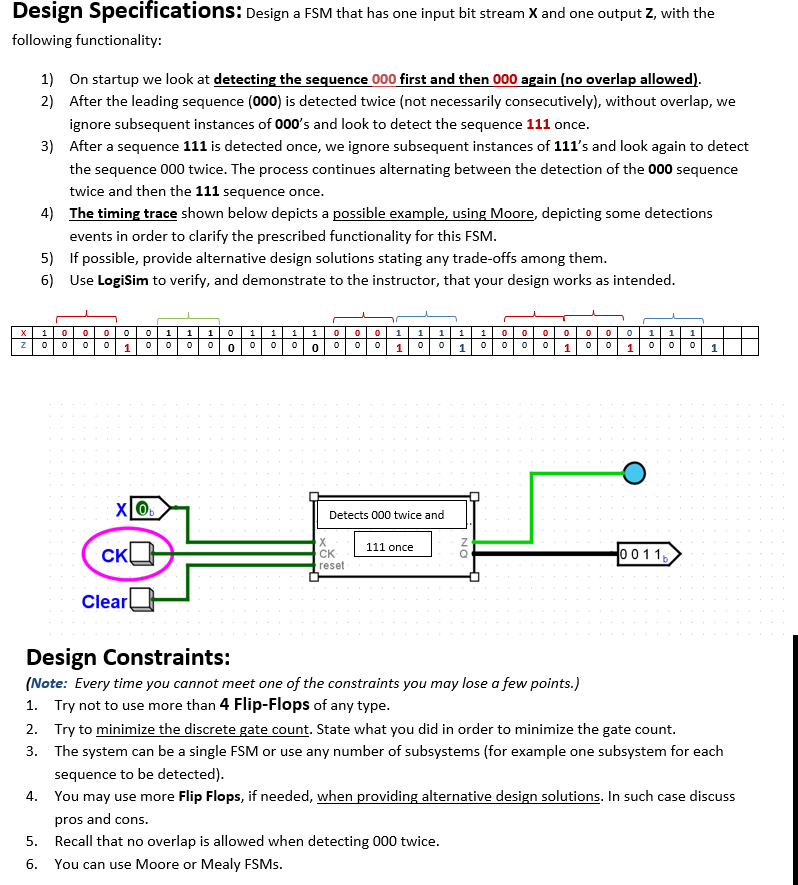

Using Logisim - evolution Please create the design. I will send you my design by text and I also provided the instructions for you to

Using Logisimevolution Please create the design. I will send you my design by text and I also provided the instructions for you to see how the design is made the instructions are the image My design follows all the instructions provided in the image I included, I just please need you to create the design for me using my design my formatmy work.

My design:

Step :

Design a FSM to detect the sequence twice without overlap.

One possible solution to meet the design constraints is to use a Mealy FSM with four states: S S S and S The input X is fed into a bit shift register.

In state S the output Z is and the shift register is cleared. If X is the FSM transitions to state S Otherwise, it stays in state S

In state S X is shifted into the register. If the register contains the sequence X where X is the last bit shifted in the FSM transitions to state S Otherwise, it transitions back to state S

In state S X is shifted again. If the register contains the sequence the FSM transitions to state S Otherwise, it transitions back to state S

In state S the output Z is indicating the detection of the sequence The shift register is cleared, and the FSM transitions back to state S

This FSM detects the sequence twice without overlap.

Explanation:

Design a FSM to detect the sequence twice without overlap.

Step :

Extend the FSM to detect the sequence once after detecting the sequence twice.

To extend the FSM to detect the sequence we can introduce two new states: S and S

In state S the output Z is and the shift register is cleared. If X is the FSM transitions to state S Otherwise, it stays in state S

In state S X is shifted into the register. If the register contains the sequence X where X is the last bit shifted in the FSM transitions to state S Otherwise, it transitions back to state S

In state S X is shifted again. If the register contains the sequence the FSM transitions to state S Otherwise, it transitions back to state S

In state S the output Z is indicating the detection of the sequence The shift register is cleared, and the FSM transitions to state S

In state S X is shifted into the register. If the register contains the sequence XX where XX are the last two bits shifted in the FSM transitions to state S Otherwise, it transitions back to state S

In state S the output Z is indicating the detection of the sequence The shift register is cleared, and the FSM transitions back to state S

This extended FSM alternates between detecting the sequence twice and then the sequence once.

Explanation:

Extend the FSM to detect the sequence once after detecting the sequence twice.

Final Answer:

The FSM design described in steps and meets the design specifications and constraints provided. It uses a total of flipflops for the shift register, and for the state representation The gate count is minimized by utilizing the Mealy FSM model and carefully designing the state transitions based on the input sequence conditions. This design can be implemented in LogiSim and verified for its intended functionality.

The instructions for the assignment are in the image provided, again my work follows these instructions and I provided the image for you to have a general idea of how the design should look. Thank you.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started