Question

What would be the expected outcome of the following instructions? [2+2 points] I1: BEQZ R1 #loop I2: ADD 4(R1) R2 R3 (the first operand is

What would be the expected outcome of the following instructions? [2+2 points] I1: BEQZ R1 #loop

I2: ADD 4(R1) R2 R3 (the first operand is the destination, and the second and third operands are source operands)

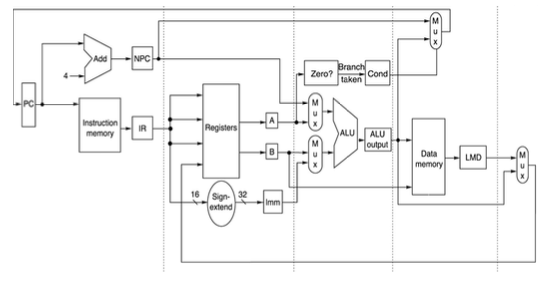

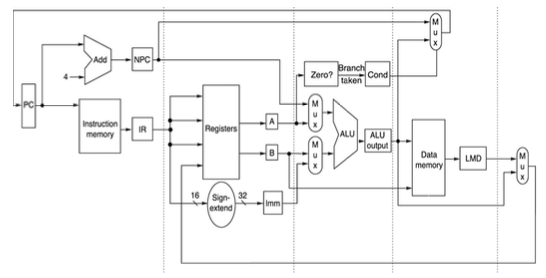

Can the MIPS datapath below handle instructions I1 and I2? [26 points] If yes, explain how. Specifically:

-

- Highlight the data lines relevant to each instruction.

-

- Indicate the data carried by all the highlighted data lines, the values stored in the relevant special purpose

registers, and the values of the control lines of the three multiplexers. If not, explain why and how you would modify the datapath to support each instruction.

I1: BEQZ R1 #loop

I2: ADD 4(R1) R2 R3

Assumptions for remaining problems

In all the problems/questions below, assume that:

-

You are operating on a 32-bit RISC processor. In particular, your architecture of reference is the MIPS processor (datapath shown in Question 2). You can use only the instructions and the addressing modes supported by the MIPS datapath and by the 3 instruction formats seen in class.

-

You are dealing only with 32-bit integer values.

-

You have available 32 integer registers (R0 to R31). You can assume that register R0 stores value 0.

-

You can use only the following instructions:

o Memory/datatransfers:LW(load),SW(store). o Arithmetic/logical: any add, subtract, multiply, divide, and, or, xor instruction (i.e., ADD, SUB,

MULT, DIV, AND, OR, XOR) o Control:BEQZ(=0),BNEZ(=0),BGTZ(>0),BGEZ(0),BLTZ(

Note that the MOV instruction is not included in the list above.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started