Question

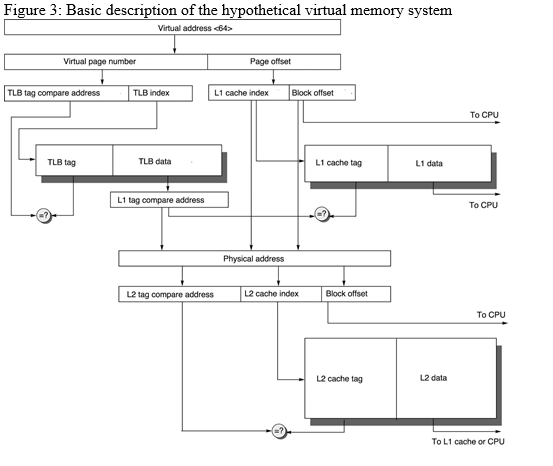

You are designing a hypothetical virtual memory system (similar to figure 1) with TLB, first-level and second-level caches. You are given the following conditions: 64-bit

You are designing a hypothetical virtual memory system (similar to figure 1) with TLB, first-level and second-level caches. You are given the following conditions:

64-bit virtual address space

41-bit physical address space

L1 cache is virtually indexed, physically tagged, and with size 8 KB

L2 cache is physical indexed, physically tagged, and with size 4 MB

Block size of both L1 and L2 caches are 64 bytes

Page size is 8 KB

L1 cache is direct-mapped, L2 cache is two-way associative

TLB is direct-mapped with 256 entries

This question continues on the next page

Calculate the number of bits needed for the following fields:

virtual page number

page offset

TLB index

TLB tag

TLB data

L1 cache index

L1 block offset

L1 Cache tag

L1 data

L2 cache index

L2 block offset

L2 Cache tag

L2 data

Figure 3: Basic description of the hypothetical virtual memory system Virtual addressStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started