Your design should generate a 100 Hz clock signal from the 50 MHz clock and use it as the clock for all other logic. Quartus

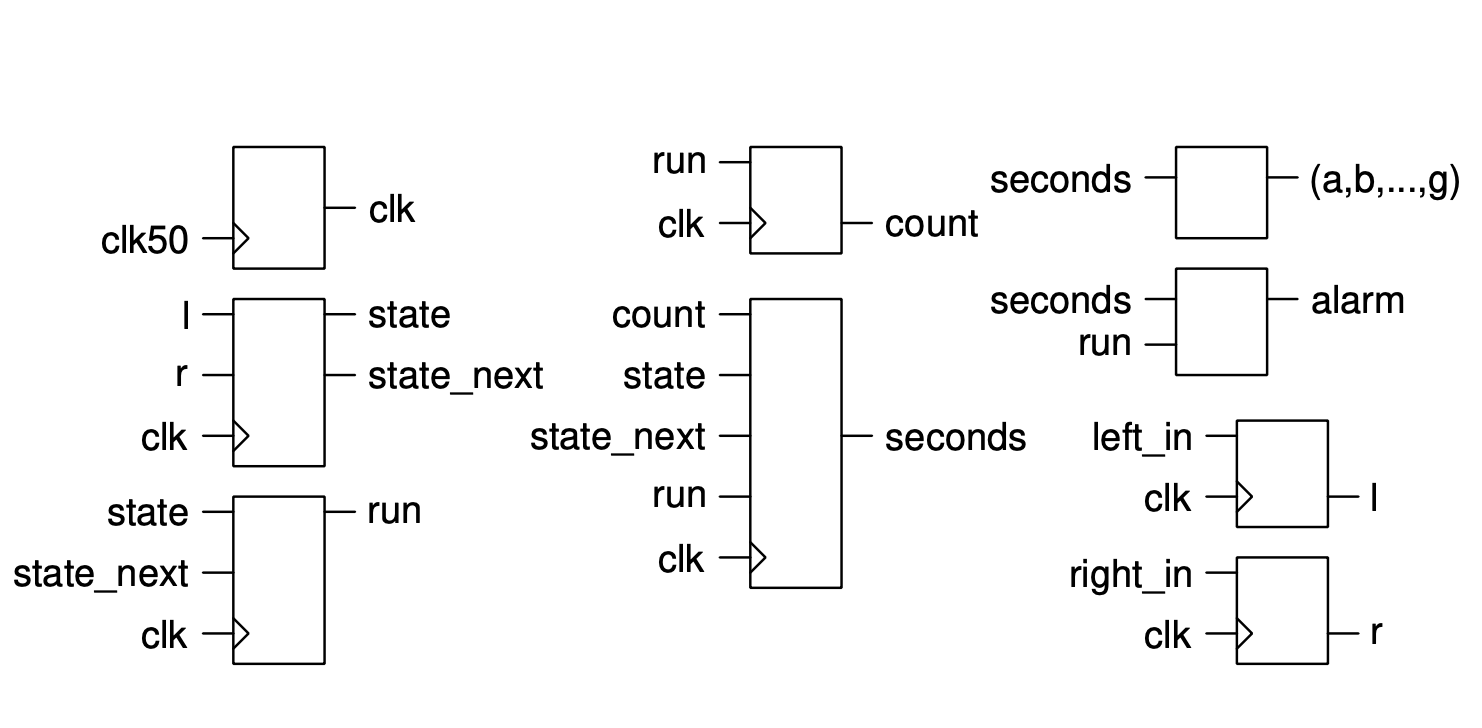

Your design should generate a 100 Hz clock signal from the 50 MHz clock and use it as the clock for all other logic. Quartus should recognize the divided clock signal as a clock.

The time remaining should be displayed as a hexadecimal digit on a 7-segment LED display instead of a 4-bit binary number. Your design should use an array as a lookup table instead of a selected or conditional assignment.

The operation of the timer should be modified so that the pushbutton switches control the timer as follows

-

pressing and releasing only the left button will cause the time to increase by 1

-

pressing and releasing only the right button will cause the time to decrease by 1

-

pressing both buttons and releasing them will toggle the run/stop state

In no case should the time remaining be decremented when at zero or incremented when at 15.

Your design should comply with the course VHDL coding guidelines including that it be synchronous all registers (except for one clock divider) should use the same clock and not use asynchronous sets or clears.

:

:

Step by Step Solution

There are 3 Steps involved in it

Step: 1

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started