Question: (a) Design a four-resistor bias network with the configuration shown in Figure P5.61 to yield (Q)-point values of (I_{C Q}=50 mu mathrm{A}) and (V_{C E

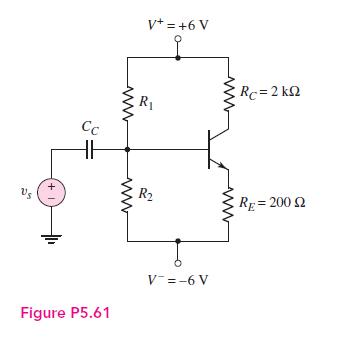

(a) Design a four-resistor bias network with the configuration shown in Figure P5.61 to yield \(Q\)-point values of \(I_{C Q}=50 \mu \mathrm{A}\) and \(V_{C E Q}=5 \mathrm{~V}\). The bias voltages are \(V^{+}=+5 \mathrm{~V}\) and \(V^{-}=-5 \mathrm{~V}\). Assume a transistor with \(\beta=80\) is available. The voltage across the emitter resistor should be approximately \(1 \mathrm{~V}\).

(b) The transistor in part (a) is replaced by one with \(\beta=120\). Determine the resulting \(Q\)-point.

+1 V+ = +6 V R Rc = 2 k www Cc HH R RE=200 2 Figure P5.61 V-=-6 V

Step by Step Solution

★★★★★

3.43 Rating (156 Votes )

There are 3 Steps involved in it

1 Expert Approved Answer

Step: 1 Unlock

Question Has Been Solved by an Expert!

Get step-by-step solutions from verified subject matter experts

Step: 2 Unlock

Step: 3 Unlock