Question: Cache organization is often influenced by the desire to reduce the cache's power consumption. For that purpose we assume that the cache is physically distributed

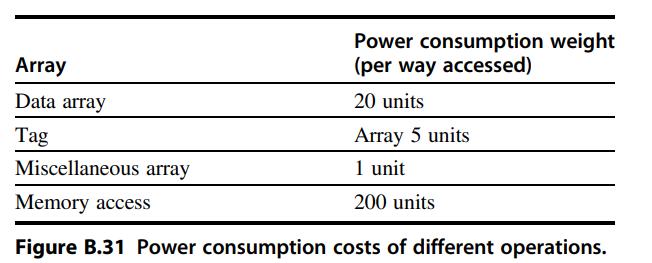

Cache organization is often influenced by the desire to reduce the cache's power consumption. For that purpose we assume that the cache is physically distributed into a data array (holding the data), a tag array (holding the tags), and replacement array (holding information needed by replacement policy). Furthermore, every one of these arrays is physically distributed into multiple subarrays (one per way) that can be individually accessed; for example, a four-way set associative least recently used (LRU) cache would have four data subarrays, four tag subarrays, and four replacement subarrays. We assume that the replacement subarrays are accessed once per access when the LRU replacement policy is used, and once per miss if the first-in, first-out (FIFO) replacement policy is used. It is not needed when a random replacement policy is used. For a specific cache, it was determined that the accesses to the different arrays have the following power consumption weights (Figure B.31):

a. A cache read hit. All arrays are read simultaneously.

b. Repeat part (a) for a cache read miss.

c. Repeat part (a) assuming that the cache access is split across two cycles. In the first cycle, all the tag subarrays are accessed. In the second cycle, only the subarray whose tag matched will be accessed.

d. Repeat part (c) for a cache read miss (no data array accesses in the second cycle).

e. Repeat part (c) assuming that logic is added to predict the cache way to be accessed. Only the tag subarray for the predicted way is accessed in cycle one. A way hit (address match in predicted way) implies a cache hit. A way miss dictates examining all the tag subarrays in the second cycle. In case of a way hit, only one data subarray (the one whose tag matched) is accessed in cycle two. Assume the way predictor hits.

f. Repeat part (e) assuming that the way predictor misses (the way it choses is wrong). When it fails, the way predictor adds an extra cycle in which it accesses all the tag subarrays. Assume the way predictor miss is followed by a cache read hit.

g. Repeat part (f) assuming a cache read miss.

h. Use parts (e), (f), and (g) for the general case where the workload has the following statistics: way predictor miss rate=5% and cache miss rate=3%. (Consider different replacement policies.)

Estimate the memory system (cache + memory) power usage (in power units) for the following configurations. We assume the cache is four-way set associative. Provide answers for the LRU, FIFO, and random replacement policies.

Array Data array Tag Power consumption weight (per way accessed) 20 units Array 5 units 1 unit 200 units Miscellaneous array Memory access Figure B.31 Power consumption costs of different operations.

Step by Step Solution

3.43 Rating (156 Votes )

There are 3 Steps involved in it

To determine the power consumption of the cache and memory system for each operation described we will calculate the power usage based on the provided power consumption weights for the data array tag ... View full answer

Get step-by-step solutions from verified subject matter experts