When processor designers consider a possible improvement to the processor datapath, the decision usually depends on the

Question:

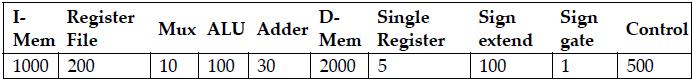

When processor designers consider a possible improvement to the processor datapath, the decision usually depends on the cost/performance trade-off. In the following three problems, assume that we are beginning with the datapath from Figure 4.21, the latencies from Exercise 4.7, and the following costs:

Suppose doubling the number of general purpose registers from 32 to 64 would reduce the number of lw and sw instruction executed by 12%, but increase the latency of the register file from 150 ps to 160 ps and double the cost from 200 to 400.

1. What is the speedup achieved by adding this improvement?

2. Compare the change in performance to the change in cost.

Data from Exercise 4.7

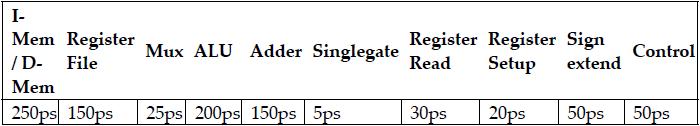

Problems in this exercise assume that the logic blocks used to implement a processor’s datapath have the following latencies:

“Register read” is the time needed after the rising clock edge for the new register value to appear on the output. This value applies to the PC only. “Register setup” is the amount of time a register’s data input must be stable before the rising edge of the clock. This value applies to both the PC and Register File.

1. What is the latency of an R-type instruction (i.e., how long must the clock period be to ensure that this instruction works correctly)?

2. What is the latency of lw? (Check your answer carefully. Many students place extra muxes on the critical path.)

3. What is the latency of sw? (Check your answer carefully. Many students place extra muxes on the critical path.)

4. What is the latency of beq?

5. What is the latency of an arithmetic, logical, or shift

I-type (non-load) instruction?

6. What is the minimum clock period for this CPU?

Figure 4.21

![PC Add Read address Instruction (31-01 Instruction [31-26] Instruction [25-21] Instruction [20-16]](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1703/7/6/8/476658d719c50eb01703768474996.jpg)

Step by Step Answer:

Computer Organization And Design MIPS Edition The Hardware/Software Interface

ISBN: 9780128201091

6th Edition

Authors: David A. Patterson, John L. Hennessy