Question: 1. (10 pts) Given a 128K byte address space, and the following memory map (layout) answer the following questions: From $00000 to $1DFFF is RAM.

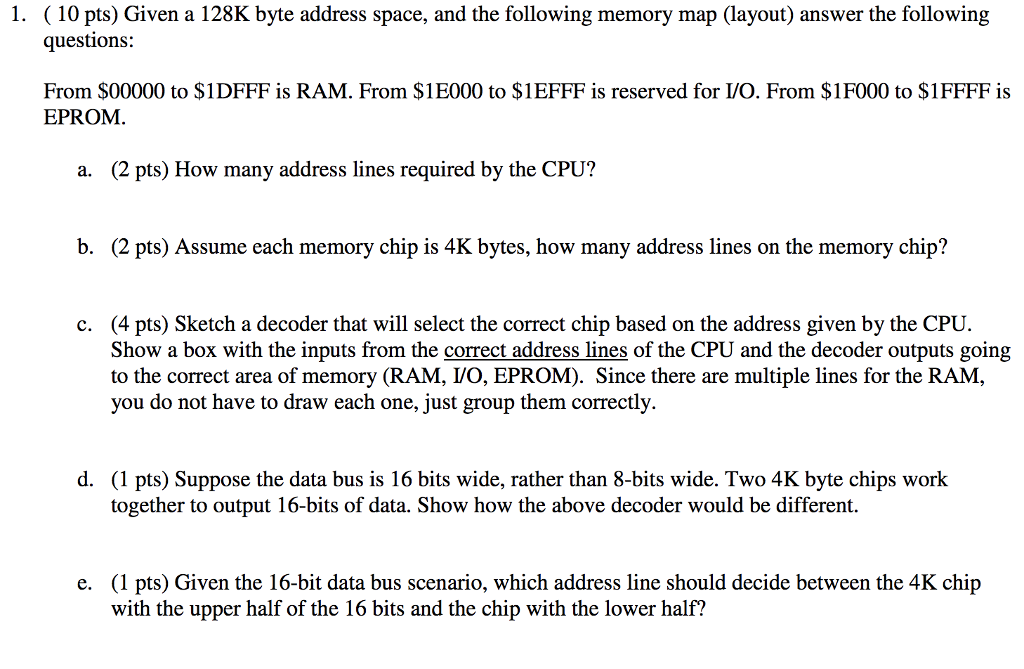

1. (10 pts) Given a 128K byte address space, and the following memory map (layout) answer the following questions: From $00000 to $1DFFF is RAM. From $1E000 to $1EFFF is reserved for I/O. From $1F000 to $1FFFF is EPROM. a. (2 pts) How many address lines required by the CPU? b. (2 pts) Assume each memory chip is 4K bytes, how many address lines on the memory chip? (4 pts) Sketch a decoder that will select the correct chip based on the address given by the CPU. Show a box with the inputs from the correct address lines of the CPU and the decoder outputs going to the correct area of memory (RAM, IO, EPROM). Since there are multiple lines for the RAM, you do not have to draw each one, just group them correctly. c. d. (1 pts) Suppose the data bus is 16 bits wide, rather than 8-bits wide. Two 4K byte chips work together to output 16-bits of data. Show how the above decoder would be different. (1 pts) Given the 16-bit data bus scenario, which address line should decide between the 4K chip with the upper half of the 16 bits and the chip with the lower half? e. 1. (10 pts) Given a 128K byte address space, and the following memory map (layout) answer the following questions: From $00000 to $1DFFF is RAM. From $1E000 to $1EFFF is reserved for I/O. From $1F000 to $1FFFF is EPROM. a. (2 pts) How many address lines required by the CPU? b. (2 pts) Assume each memory chip is 4K bytes, how many address lines on the memory chip? (4 pts) Sketch a decoder that will select the correct chip based on the address given by the CPU. Show a box with the inputs from the correct address lines of the CPU and the decoder outputs going to the correct area of memory (RAM, IO, EPROM). Since there are multiple lines for the RAM, you do not have to draw each one, just group them correctly. c. d. (1 pts) Suppose the data bus is 16 bits wide, rather than 8-bits wide. Two 4K byte chips work together to output 16-bits of data. Show how the above decoder would be different. (1 pts) Given the 16-bit data bus scenario, which address line should decide between the 4K chip with the upper half of the 16 bits and the chip with the lower half? e

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts