Question: Consider an initial single-cycle MIPS processor with a cycle-time of 1600ps and a multicycle design with the following properties: 1) a cycle time of

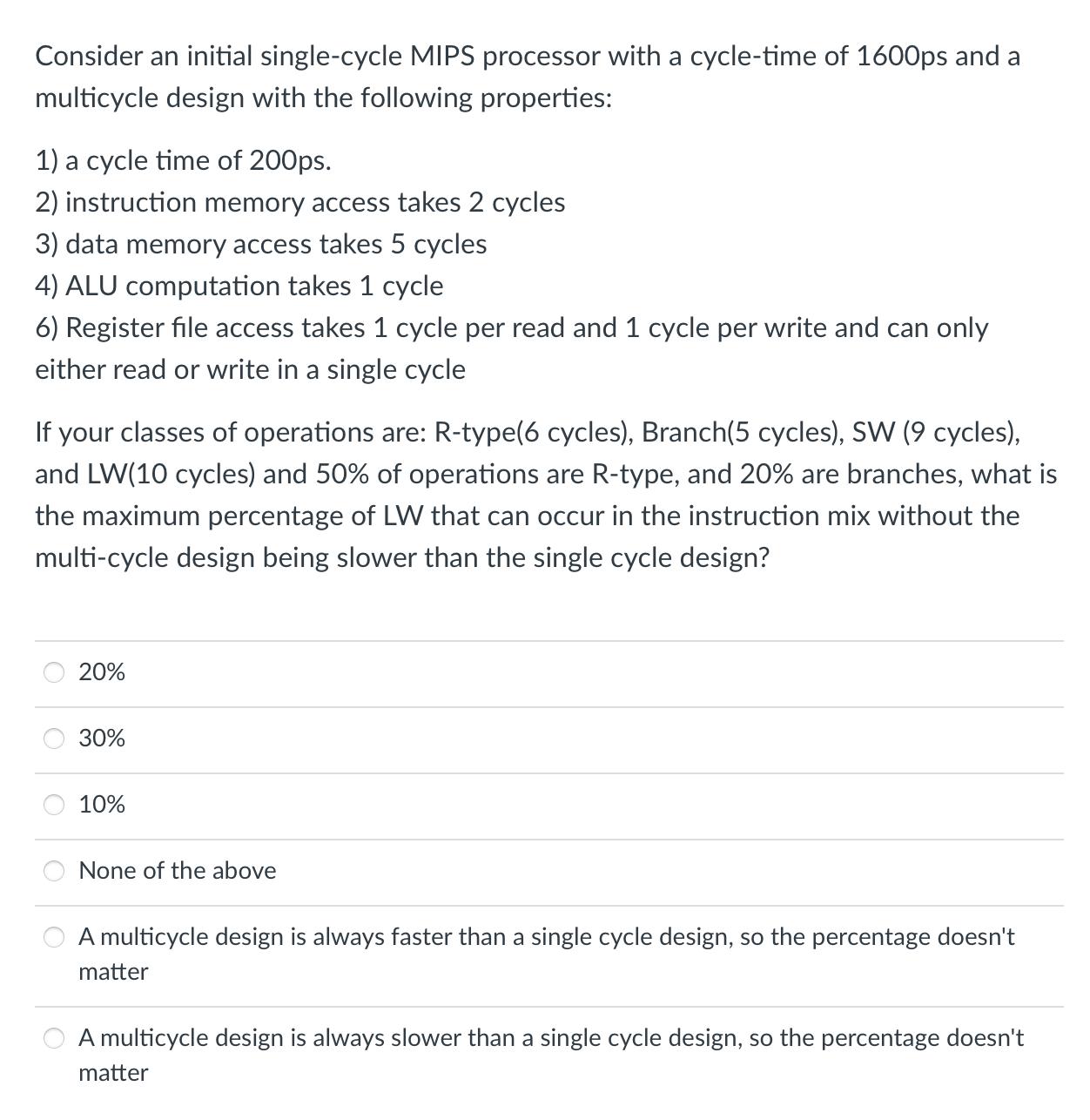

Consider an initial single-cycle MIPS processor with a cycle-time of 1600ps and a multicycle design with the following properties: 1) a cycle time of 200ps. 2) instruction memory access takes 2 cycles 3) data memory access takes 5 cycles 4) ALU computation takes 1 cycle 6) Register file access takes 1 cycle per read and 1 cycle per write and can only either read or write in a single cycle If your classes of operations are: R-type(6 cycles), Branch(5 cycles), SW (9 cycles), and LW(10 cycles) and 50% of operations are R-type, and 20% are branches, what is the maximum percentage of LW that can occur in the instruction mix without the multi-cycle design being slower than the single cycle design? 20% 30% 10% None of the above A multicycle design is always faster than a single cycle design, so the percentage doesn't matter A multicycle design is always slower than a single cycle design, so the percentage doesn't matter

Step by Step Solution

3.46 Rating (153 Votes )

There are 3 Steps involved in it

Solution Ans A multicycle design is always f... View full answer

Get step-by-step solutions from verified subject matter experts