Answered step by step

Verified Expert Solution

Question

1 Approved Answer

digital system design with fgpa i need solution ASAP Objective: The objective of this lab is to introduce the student to parameterized modules in Altera

digital system design with fgpa i need solution ASAP

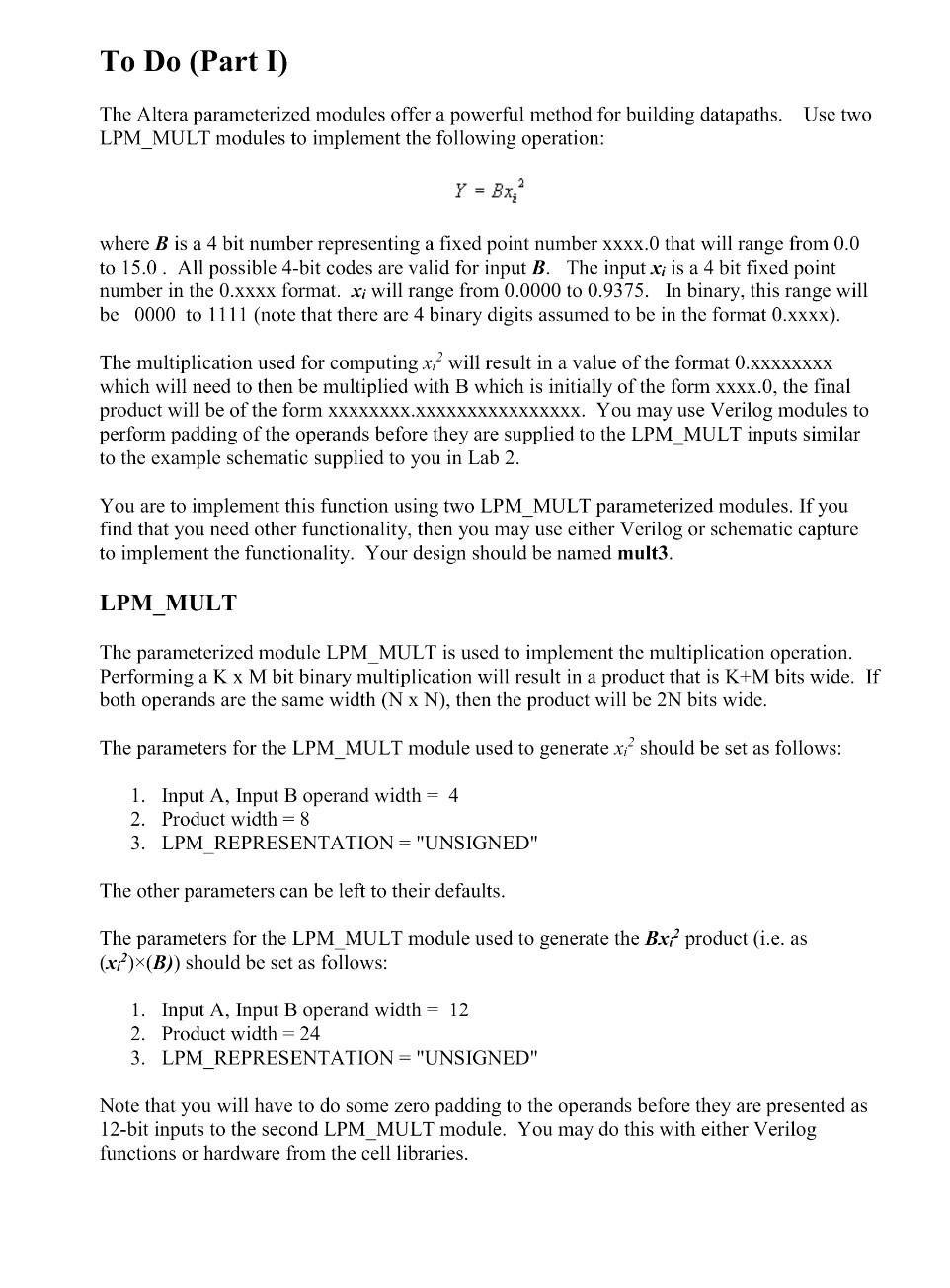

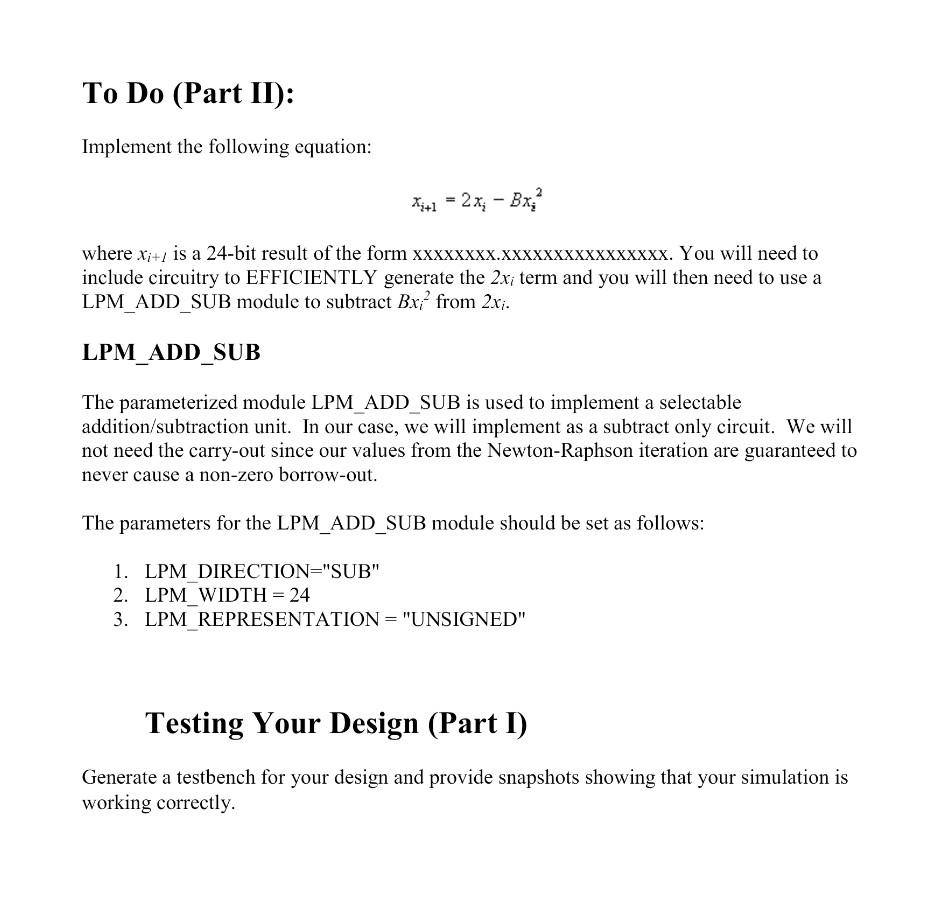

Objective: The objective of this lab is to introduce the student to parameterized modules in Altera and to use these modules to implement a simple datapath. Background The division operation is one of the most computationally expensive operations in Arithmetic Logic Units (ALUs). There are several methods for performing division by using a multiplier. One way to do it is as follows: BA=A(B1) In this way, a multiplier circuit can be used if there is some way to compute the reciprocal value of the divisor, B. The Newton-Raphson iteration equation is one way to compute the inverse of a value. This technique starts with a "guess" or "estimate" of the inverse and refines the estimate in an iterative manner. This is usually implemented by including a memory that contains the initial estimates of the reciprocal and using several of the most significant bits of the divisor as address lines for the memory. This is commonly called a "ROM Reciprocal Table". This initial estimate of (1/B) is then the first x0 value in the Newton-Raphson iteration equation shown below: xi+1=xi+xi(1Bxi) As an example, if it is desired to find an approximation for 1/9 and we begin with an estimate of x0=0.1 (that is 1/10 ), the following values result: In this laboratory, you will implement the logic for computing a single iteration of the Newton-Raphson equation. We will implement the equation in the following form: xi+1=xi+xi(1Bxi)=2xiBxi2 To Do (Part I) The Altera parameterized modules offer a powerful method for building datapaths. Use two LPM_MULT modules to implement the following operation: Y=Bxi2 where B is a 4 bit number representing a fixed point number xxxx.0 that will range from 0.0 to 15.0 . All possible 4-bit codes are valid for input B. The input xi is a 4 bit fixed point number in the 0.xxx format. xi will range from 0.0000 to 0.9375. In binary, this range will be 0000 to 1111 (note that there are 4 binary digits assumed to be in the format 0 .xxxx). The multiplication used for computing xi2 will result in a value of the format 0.xxxx which will need to then be multiplied with B which is initially of the form xxxx.0, the final perform padding of the operands before they are supplied to the LPM_MULT inputs similar to the example schematic supplied to you in Lab 2. You are to implement this function using two LPM_MULT parameterized modules. If you find that you need other functionality, then you may use either Verilog or schematic capture to implement the functionality. Your design should be named mult3. LPM_MULT The parameterized module LPM_MULT is used to implement the multiplication operation. Performing a KM bit binary multiplication will result in a product that is K+M bits wide. If both operands are the same width (NxN), then the product will be 2N bits wide. The parameters for the LPM_MULT module used to generate xi2 should be set as follows: 1. Input A, Input B operand width =4 2. Product width =8 3. LPM_REPRESENTATION = "UNSIGNED" The other parameters can be left to their defaults. The parameters for the LPM_MULT module used to generate the Bxi2 product (i.e. as (xi2)(B)) should be set as follows: 1. Input A, Input B operand width =12 2. Product width =24 3. LPM_REPRESENTATION = "UNSIGNED" Note that you will have to do some zero padding to the operands before they are presented as 12-bit inputs to the second LPM_MULT module. You may do this with either Verilog functions or hardware from the cell libraries. Implement the following equation: xi+1=2xiBxi2 where xi+1 is a 24-bit result of the form xxxxxxxx.xxxxxxxxxxxxxxxx. You will need to include circuitry to EFFICIENTLY generate the 2xi term and you will then need to use a LPM_ADD_SUB module to subtract Bxi2 from 2xi. LPM_ADD_SUB The parameterized module LPM_ADD_SUB is used to implement a selectable addition/subtraction unit. In our case, we will implement as a subtract only circuit. We will not need the carry-out since our values from the Newton-Raphson iteration are guaranteed to never cause a non-zero borrow-out. The parameters for the LPM_ADD_SUB module should be set as follows: 1. LPM_DIRECTION="SUB" 2. LPM_WIDTH =24 3. LPM_REPRESENTATION = "UNSIGNED" Testing Your Design (Part I) Generate a testbench for your design and provide snapshots showing that your simulation is working correctly

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started