Question: Please Answer The Following Quesiton. Include all parts, show steps clearly. 2 As mentioned in class, the ring oscillator is a circuit consisting of an

Please Answer The Following Quesiton. Include all parts, show steps clearly. 2

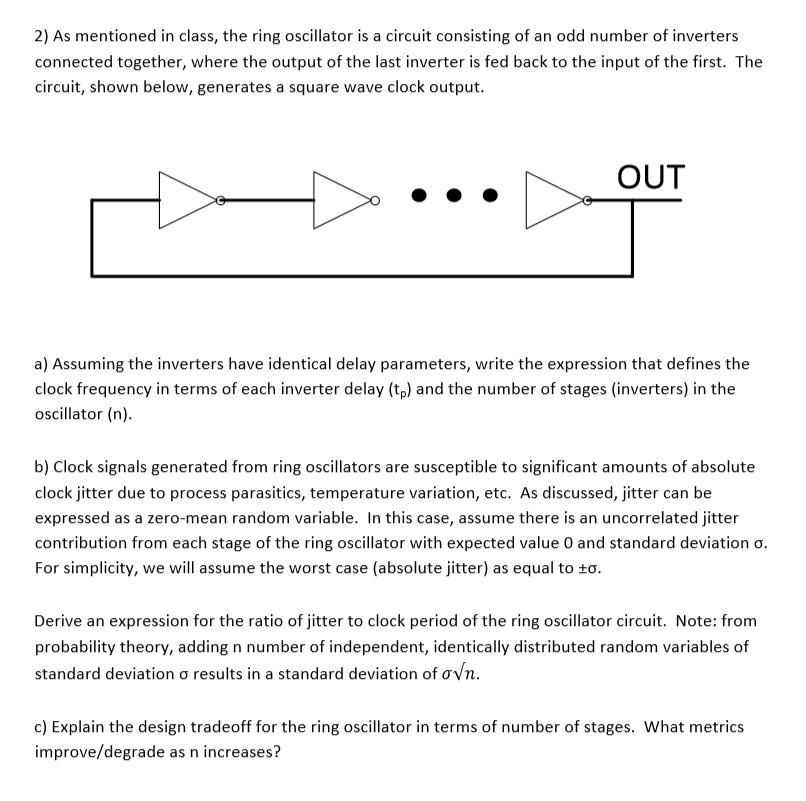

As mentioned in class, the ring oscillator is a circuit consisting of an odd number of inverters connected together, where the output of the last inverter is fed back to the input of the first. The circuit, shown below, generates a square wave clock output. Assuming the inverters have identical delay parameters, write the expression that defines the clock frequency in terms of each inverter delay (t_p) and the number of stages (inverters) in the oscillator (n). Clock signals generated from ring oscillators are susceptible to significant amounts of absolute clock jitter due to process parasitics, temperature variation, etc. As discussed, jitter can be expressed as a zero-mean random variable. In this case, assume there is an uncorrelated jitter contribution from each stage of the ring oscillator with expected value 0 and standard deviation a. For simplicity, we will assume the worst case (absolute jitter) as equal to plusminus sigma. Derive an expression for the ratio of jitter to clock period of the ring oscillator circuit. Explain the design tradeoff for the ring oscillator in terms of number of stages. What metrics improve/degrade as n increases? As mentioned in class, the ring oscillator is a circuit consisting of an odd number of inverters connected together, where the output of the last inverter is fed back to the input of the first. The circuit, shown below, generates a square wave clock output. Assuming the inverters have identical delay parameters, write the expression that defines the clock frequency in terms of each inverter delay (t_p) and the number of stages (inverters) in the oscillator (n). Clock signals generated from ring oscillators are susceptible to significant amounts of absolute clock jitter due to process parasitics, temperature variation, etc. As discussed, jitter can be expressed as a zero-mean random variable. In this case, assume there is an uncorrelated jitter contribution from each stage of the ring oscillator with expected value 0 and standard deviation a. For simplicity, we will assume the worst case (absolute jitter) as equal to plusminus sigma. Derive an expression for the ratio of jitter to clock period of the ring oscillator circuit. Explain the design tradeoff for the ring oscillator in terms of number of stages. What metrics improve/degrade as n increases

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts