Question: please i need answer within an hour A pipeline hazard: O Occurs when the pipeline, or some portion of the pipeline, must stall because conditions

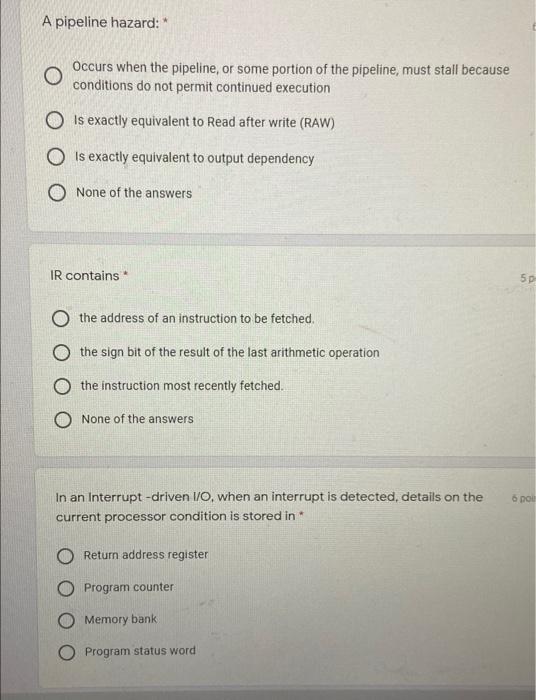

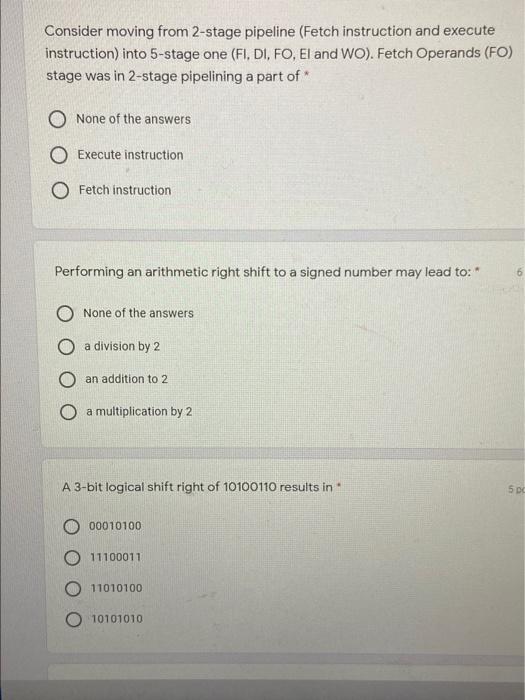

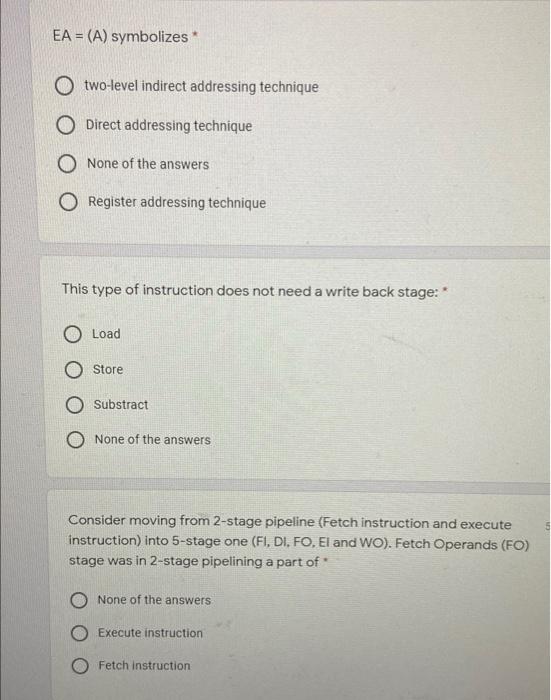

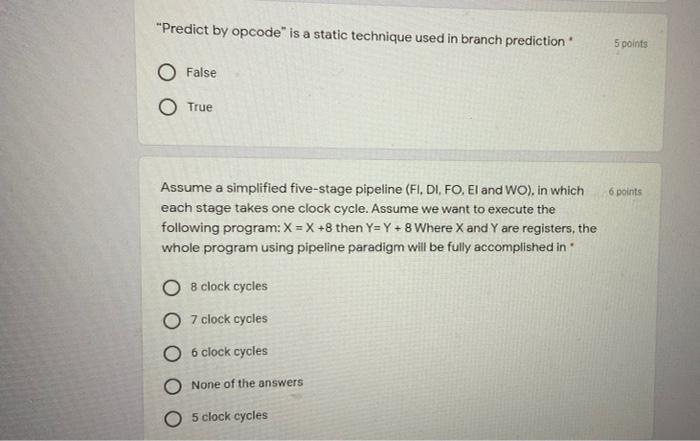

A pipeline hazard: O Occurs when the pipeline, or some portion of the pipeline, must stall because conditions do not permit continued execution Is exactly equivalent to Read after write (RAW) O is exactly equivalent to output dependency None of the answers IR contains 5p the address of an instruction to be fetched. the sign bit of the result of the last arithmetic operation the instruction most recently fetched. None of the answers 6 Dol In an Interrupt-driven I/O, when an interrupt is detected, details on the current processor condition is stored in Return address register Program counter Memory bank Program status word Consider moving from 2-stage pipeline (Fetch instruction and execute instruction) into 5-stage one (FI, DI, FO, El and WO). Fetch Operands (FO) stage was in 2-stage pipelining a part of O None of the answers O Execute instruction O Fetch instruction Performing an arithmetic right shift to a signed number may lead to: None of the answers a division by 2 an addition to 2 O a multiplication by 2 A 3-bit logical shift right of 10100110 results in 5 DC 00010100 O 11100011 11010100 010101010 EA = (A) symbolizes O two-level indirect addressing technique O Direct addressing technique O None of the answers O Register addressing technique This type of instruction does not need a write back stage: Load Store Substract None of the answers Consider moving from 2-stage pipeline (Fetch instruction and execute instruction) into 5-stage one (FI, DI, FO, El and WO). Fetch Operands (FO) stage was in 2-stage pipelining a part of None of the answers O Execute instruction Fetch instruction "Predict by opcode" is a static technique used in branch prediction 5 points False O True 6 points Assume a simplified five-stage pipeline (FI, DI, FO, El and WO), in which each stage takes one clock cycle. Assume we want to execute the following program: X = X +8 then Y=Y+8 Where X and Y are registers, the whole program using pipeline paradigm will be fully accomplished in 8 clock cycles O 7 clock cycles O 6 clock cycles None of the answers 5 clock cycles

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts