Question: Please look at the inputs from question 1. Also see 6(r) vs 60, other posted questions do not apply to this. I only need question

Please look at the inputs from question 1. Also see 6(r) vs 60, other posted questions do not apply to this.

I only need question 2.

Thank you

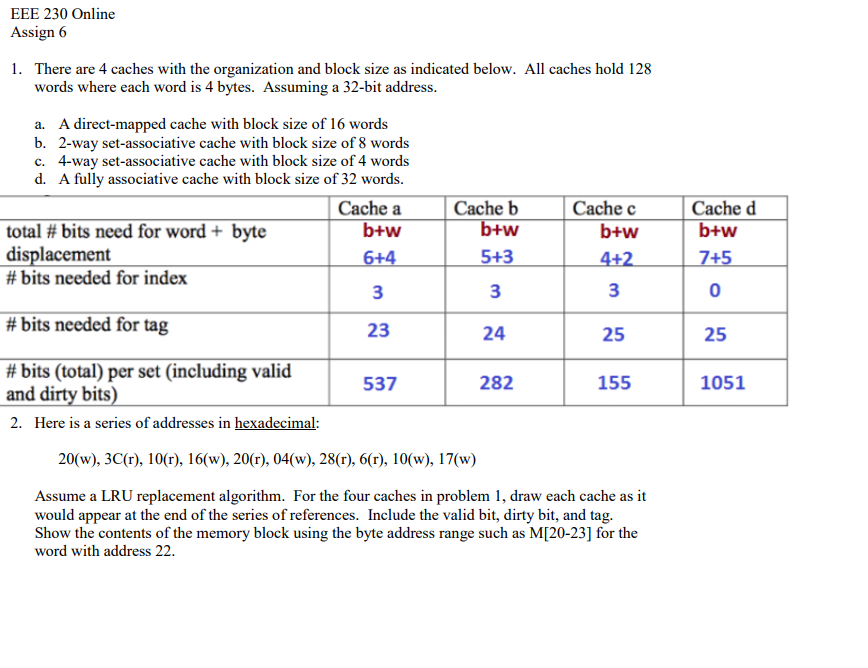

EEE 230 Online Assign 6 There are 4 caches with the organization and block size as indicated below. All caches hold 128 words where each word is 4 bytes. Assuming a 32-bit address 1. a. b. c. d. A direct-mapped cache with block size of 16 words 2-way set-associative cache with block size of 8 words 4-way set-associative cache with block size of 4 words A fully associative cache with block size of 32 words Cache a b+w Cache c b+w Cache d b+w Cache b total # bits need for word + byte displacement # bits needed for index 5+3 3 23 537 0 25 1051 # bits needed for tag 24 25 # bits (total) per set (including valid and dirty bits) 2. Here is a series of addresses in hexadecimal 282 155 20(w), 3C(r), 10(r), 16(w), 20(r), 04(w), 28(r), 6(r), 10(w), 17(w) Assume a LRU replacement algorithm. For the four caches in problem 1, draw each cache as it would appear at the end of the series of references. Include the valid bit, dirty bit, and tag. Show the contents of the memory block using the byte address range such as M[20-23] for the word with address 22 EEE 230 Online Assign 6 There are 4 caches with the organization and block size as indicated below. All caches hold 128 words where each word is 4 bytes. Assuming a 32-bit address 1. a. b. c. d. A direct-mapped cache with block size of 16 words 2-way set-associative cache with block size of 8 words 4-way set-associative cache with block size of 4 words A fully associative cache with block size of 32 words Cache a b+w Cache c b+w Cache d b+w Cache b total # bits need for word + byte displacement # bits needed for index 5+3 3 23 537 0 25 1051 # bits needed for tag 24 25 # bits (total) per set (including valid and dirty bits) 2. Here is a series of addresses in hexadecimal 282 155 20(w), 3C(r), 10(r), 16(w), 20(r), 04(w), 28(r), 6(r), 10(w), 17(w) Assume a LRU replacement algorithm. For the four caches in problem 1, draw each cache as it would appear at the end of the series of references. Include the valid bit, dirty bit, and tag. Show the contents of the memory block using the byte address range such as M[20-23] for the word with address 22

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts