Question

//Tester module sends a periodic clock signal to the flip-flop module tester(q,qn,clk,d, A , B, ALUctl); input q,qn; output clk,d; //A, B, ALUctl; output [3:0]

//Tester module sends a periodic clock signal to the flip-flop module tester(q,qn,clk,d, A , B, ALUctl); input q,qn; output clk,d; //A, B, ALUctl; output [3:0] A, B, ALUctl; reg clk,d, A, B, ALUctl;

//Run the test once initial begin clk=0; //Dump results of the simulation to ff.cvd $dumpfile("dff2.vcd"); $dumpvars; //Generate input signal d d=0; #9 d=1; #1 d=0; #1 d=1; #2 d=0; #1 d=1; #12 d=0; #1 d=1; #2 d=0; #1 d=1; #1 d=0; #1 d=1; #1 d=0; # 7 d=1; #8 $finish; //A=4'b0001; end

//Generate periodic clock signal always begin #4 clk=!clk; A

//Test bench connects the flip-flop to the tester module module testbench; wire clk,d,q,qn,ALzero; wire [3:0] ALUctl, A, B, ALUout; dff ff1(d,clk,q,qn); tester tst1(q,qn,clk,d, A, B, ALUctl); //parameter ALUctl = 4'b0001, state2 = 4'b0010, // state3 = 4'b0100, state4 = 4'b1000; MIPSALU alu(ALUctl,A,B,ALUout,ALzero); endmodule

module MIPSALU (ALUctl, A, B, ALUOut, Zero); input [3:0] ALUctl; input [31:0] A, B; output reg [31: 0] ALUOut; output Zero;

assign Zero = (ALUOut==0);// Zero is true if ALU0ut is 0 always @(ALUctl, A, B) begin // reevaluate if these change case (ALUctl) 0: ALUOut

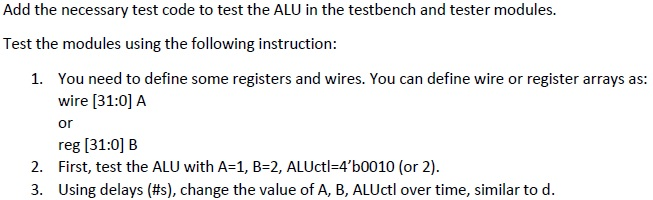

default: ALUOut Add the necessary test code to test the ALU in the testbench and tester modules. Test the modules using the following instruction 1. You need to define some registers and wires. You can define wire or register arrays as wire [31:0] A or reg [31:0] B 2. First, test the ALU with A-1, B 32, ALUctE4 b0010 (or 2). 3. Using delays (#s), change the value of A, B, ALUctl over time, similar to d. Add the necessary test code to test the ALU in the testbench and tester modules. Test the modules using the following instruction 1. You need to define some registers and wires. You can define wire or register arrays as wire [31:0] A or reg [31:0] B 2. First, test the ALU with A-1, B 32, ALUctE4 b0010 (or 2). 3. Using delays (#s), change the value of A, B, ALUctl over time, similar to d

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started