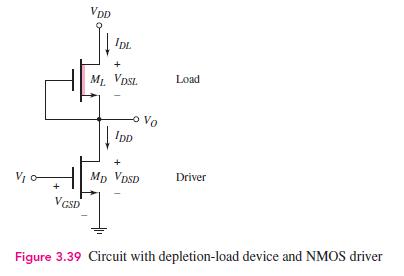

Consider the circuit in Figure 3.39 with a depletion load. Assume the circuit is biased at (V_{D

Question:

Consider the circuit in Figure 3.39 with a depletion load. Assume the circuit is biased at \(V_{D D}=3.3 \mathrm{~V}\), and assume transistor threshold voltages of \(V_{T N D}=0.4 \mathrm{~V}\) and \(V_{T N L}=-0.75 \mathrm{~V}\). Also assume \(k_{n}^{\prime}=80 \mu \mathrm{A} / \mathrm{V}^{2}\). Design the circuit such that \(V_{O}=0.05 \mathrm{~V}\) when \(V_{I}=3.3 \mathrm{~V}\) and that the maximum power dissipation is \(150 \mu \mathrm{W}\).

Figure 3.39:-

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Microelectronics Circuit Analysis And Design

ISBN: 9780071289474

4th Edition

Authors: Donald A. Neamen

Question Posted: