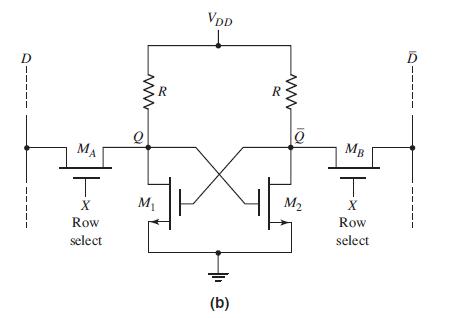

Consider the NMOS RAM cell with resistor load in Figure 16.74(b). Assume parameters values of (k_{n}^{prime}=80 mu

Question:

Consider the NMOS RAM cell with resistor load in Figure 16.74(b). Assume parameters values of \(k_{n}^{\prime}=80 \mu \mathrm{A} / \mathrm{V}^{2}, V_{T N}=0.4 \mathrm{~V}, V_{D D}=2.5 \mathrm{~V}\), and \(R=1 \mathrm{M} \Omega\).

(a) Design the width-to-length ratio of the driver transistor such that \(V_{D S}=20 \mathrm{mV}\) for the on transistor.

(b) Consider a \(16-\mathrm{K}\) memory with the cell described in part (a). Determine the standby cell current and the total memory power dissipation for a standby voltage of \(V_{D D}=1.2 \mathrm{~V}\).

Figure 16.74(b):-

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Microelectronics Circuit Analysis And Design

ISBN: 9780071289474

4th Edition

Authors: Donald A. Neamen

Question Posted: