Question: For the flip-flops in the counter in Figure 5.24, assume that t su = 3 ns, t h = 1 ns, and the propagation delay

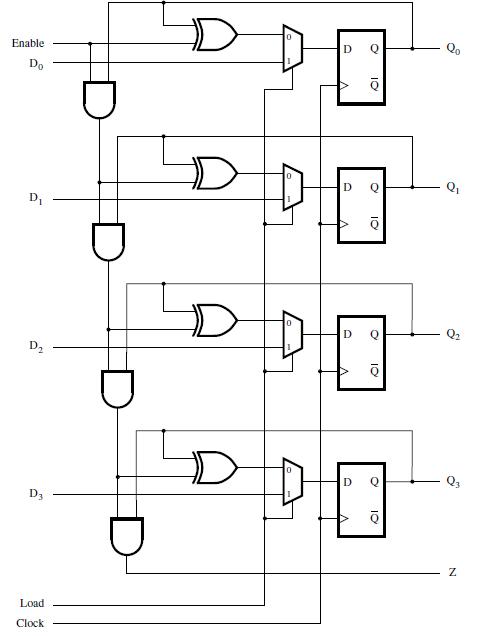

For the flip-flops in the counter in Figure 5.24, assume that tsu = 3 ns, th = 1 ns, and the propagation delay through a flip-flop is 1 ns. Assume that each AND gate, XOR gate, and 2-to-1 multiplexer has the propagation delay equal to 1 ns. What is the maximum clock frequency for which the circuit will operate correctly?

Enable Do D D D3 Load Clock D D D D D Q OI O 10 O 10 0 10 Q Z

Step by Step Solution

3.38 Rating (167 Votes )

There are 3 Steps involved in it

The maximum clock frequency for which the circuit will op... View full answer

Get step-by-step solutions from verified subject matter experts