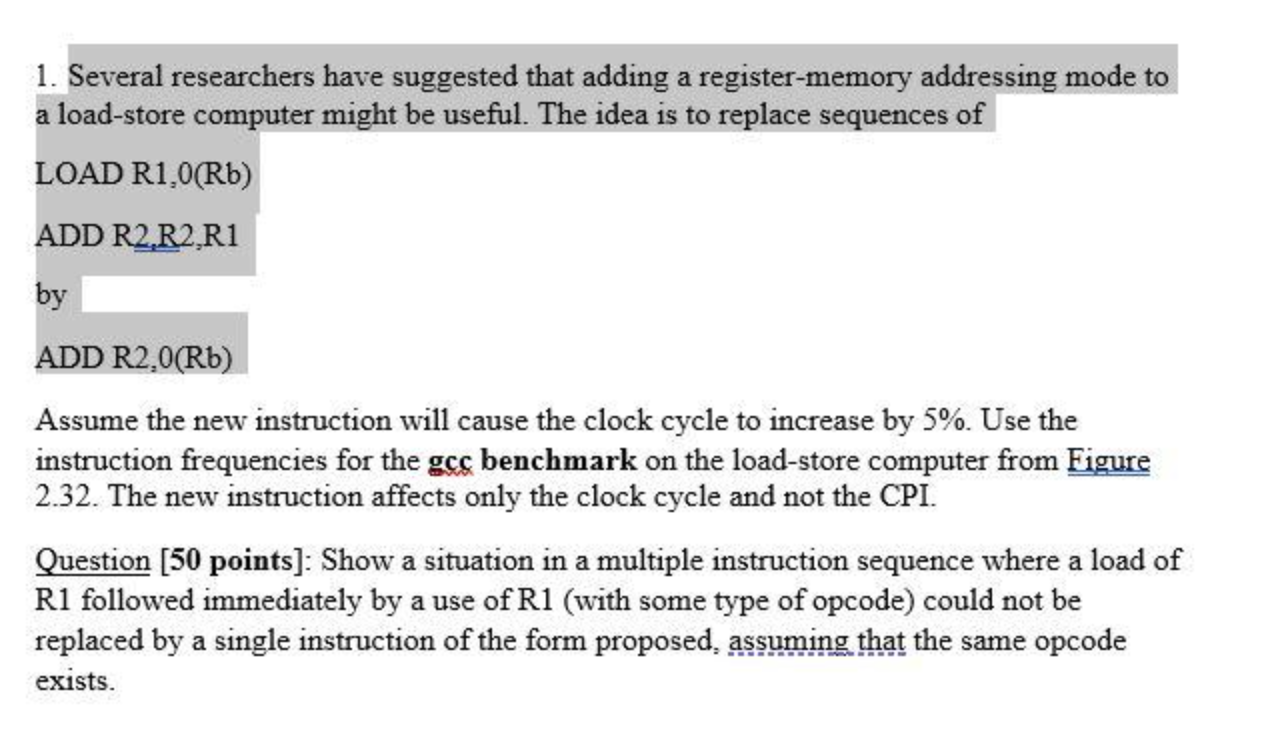

Question: 1. Several researchers have suggested that adding a register-memory addressing mode to a load-store computer might be useful. The idea is to replace sequences of

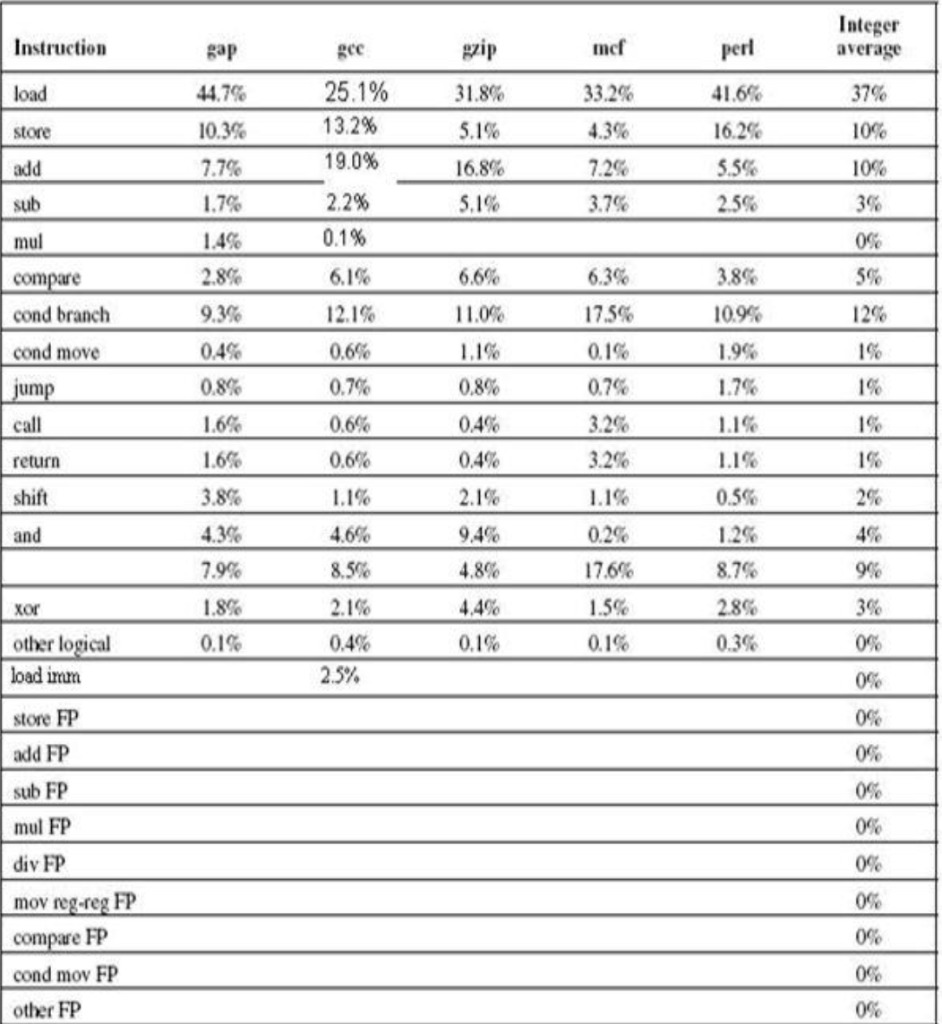

1. Several researchers have suggested that adding a register-memory addressing mode to a load-store computer might be useful. The idea is to replace sequences of LOAD R1,0(Ro) ADD R2 R2,R1 by ADD R2.0(Rb) Assume the new instruction will cause the clock cycle to increase by 5%. Use the instruction frequencies for the gcc benchmark on the load-store computer from Figure 2.32. The new instruction affects only the clock cycle and not the CPI. Question (50 points]: Show a situation in a multiple instruction sequence where a load of R1 followed immediately by a use of R1 (with some type of opcode) could not be replaced by a single instruction of the form proposed, assuming that the same opcode exists. Integer average Instruction gap mcf perl load 31.8% 33.2% 41.6% 37% store 25.1% 13.2% 19.0% 5.1% 4.3% 16.2% 10% 10.3% 7.7% 1.7% add 5.5% 10% 16.8% 5.1% 7.2% 3.7% sub 2.5% 3% 2.2% 0.1% mul OS 5% 2.8% 6.1% 6.6% 3.8% compare cond branch 9.3% 12.1% 11.0% 10.9% 12% cond move jump 0.4% 0.8% 1.6% 0.6% 0.7% 1.1% 0.8% 6.3% 17.5% 0.1% 0.7% 3.2% 3.2% 1.95 1.7% 1% call 0.6% 0.4% 1.14 1% return 1.6% 0.6% 0.4% 1.1% 16 shift 3.8% 1.1% 2.1% 0.5% 2% and 4.6% 4 1.26 8.7% 7.9% 8.5% 4.8% 9% 0.2% 17.6% 1.5% 0.1% xor 1.8% 2.1% 2.8% 3% 4.4% 0.1% 0.1% 0.3% 0% other logical load imm 0.4% 2.5% 0% store FP add FP 0% sub FP 0% mul FP 0% div FP 0% 0% mov reg.reg FP compare FP cond mov FP 0% 0% other FP 0% 1. Several researchers have suggested that adding a register-memory addressing mode to a load-store computer might be useful. The idea is to replace sequences of LOAD R1,0(Ro) ADD R2 R2,R1 by ADD R2.0(Rb) Assume the new instruction will cause the clock cycle to increase by 5%. Use the instruction frequencies for the gcc benchmark on the load-store computer from Figure 2.32. The new instruction affects only the clock cycle and not the CPI. Question (50 points]: Show a situation in a multiple instruction sequence where a load of R1 followed immediately by a use of R1 (with some type of opcode) could not be replaced by a single instruction of the form proposed, assuming that the same opcode exists. Integer average Instruction gap mcf perl load 31.8% 33.2% 41.6% 37% store 25.1% 13.2% 19.0% 5.1% 4.3% 16.2% 10% 10.3% 7.7% 1.7% add 5.5% 10% 16.8% 5.1% 7.2% 3.7% sub 2.5% 3% 2.2% 0.1% mul OS 5% 2.8% 6.1% 6.6% 3.8% compare cond branch 9.3% 12.1% 11.0% 10.9% 12% cond move jump 0.4% 0.8% 1.6% 0.6% 0.7% 1.1% 0.8% 6.3% 17.5% 0.1% 0.7% 3.2% 3.2% 1.95 1.7% 1% call 0.6% 0.4% 1.14 1% return 1.6% 0.6% 0.4% 1.1% 16 shift 3.8% 1.1% 2.1% 0.5% 2% and 4.6% 4 1.26 8.7% 7.9% 8.5% 4.8% 9% 0.2% 17.6% 1.5% 0.1% xor 1.8% 2.1% 2.8% 3% 4.4% 0.1% 0.1% 0.3% 0% other logical load imm 0.4% 2.5% 0% store FP add FP 0% sub FP 0% mul FP 0% div FP 0% 0% mov reg.reg FP compare FP cond mov FP 0% 0% other FP 0%

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts