Answered step by step

Verified Expert Solution

Question

1 Approved Answer

Can you please do 2 and 6 Gmail 1:57 PM Sun Feb 28 15% Not Secure files.hostgator.co.in 23 of 103 Chapter 2: General-purpose processors: Software

Can you please do 2 and 6

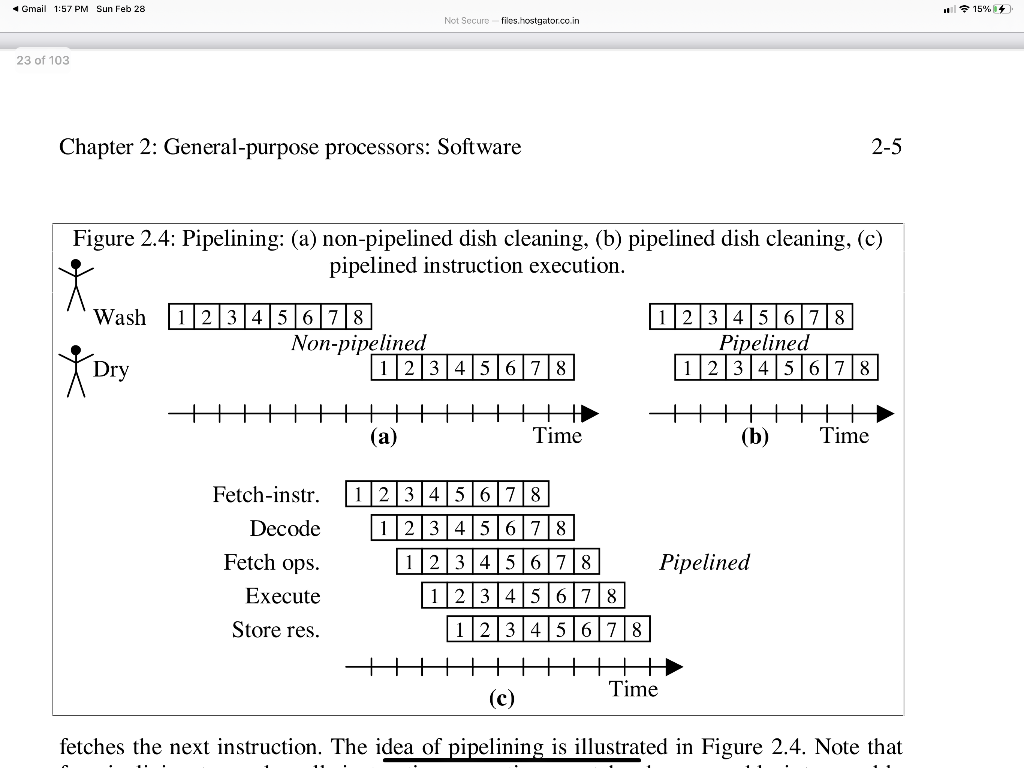

Gmail 1:57 PM Sun Feb 28 15% Not Secure files.hostgator.co.in 23 of 103 Chapter 2: General-purpose processors: Software 2-5 Figure 2.4: Pipelining: (a) non-pipelined dish cleaning, (b) pipelined dish cleaning, (c) pipelined instruction execution. Wash * 12345678 Non-pipelined 1|2|3|4|5|678 Pipelined 12345678 Dry 45678 + Time (a) (b) Time Fetch-instr. Decode Fetch ops. 1 2 3 4 5 6 7 8 1 2 3 4 5 6 7 8 1 2 3 4 5 6 7 8 1 2 3 4 5 6 7 8 12345678 Pipelined Execute Store res. + Time (c) fetches the next instruction. The idea of pipelining is illustrated in Figure 2.4. Note that 12:16 PM Sun Feb 28 al 22% Not Secure files.hostgator.co.in 33 of 103 2.9 Exercises 1. Describe why a general-purpose processor could cost less than a single-purpose processor you design yourself. 2. Detail the stages of executing the MOV instructions of Figure 2.4, assuming an 8-bit processor and a 16-bit IR and program memory following the model of Figure 2.1. Example: the stages for the ADD instruction are -- (1) fetch M[PC] into IR, (2) read Rn and Rm from register file through ALU configured for ADD, storing results back in Rn. 3. Add one instruction to the instruction set of Figure 2.4 that would reduce the size our summing assembly program by 1 instruction. (Hint: add a new branch instruction). Show the reduced program. 4. Create a table listing the address spaces for the following address sizes: (a) 8-bit, (b) 16-bit, (c) 24-bit, (d) 32-bit, (e) 64-bit. 5. Illustrate how program and data memory fetches can be overlapped in a Harvard architecture. 6. Read the entire problem before beginning: (a) Write a C program that clears an array "short int M[256]." In other words, the program sets every location to 0. Hint: your program should only be a couple lines long. (b) Assuming M starts at location 256 (and thus ends at location 511), write the same program in assembly language using the earlier instruction set. (c) Measure the time it takes you to perform parts a and b, and report those times. 7. Acquire a databook for a microcontroller. List the features of the basic version of that microcontroller, including key characteristics of the instruction set (number of instructions of each type, length per instruction, etc.), memory architecture and Gmail 1:57 PM Sun Feb 28 15% Not Secure files.hostgator.co.in 23 of 103 Chapter 2: General-purpose processors: Software 2-5 Figure 2.4: Pipelining: (a) non-pipelined dish cleaning, (b) pipelined dish cleaning, (c) pipelined instruction execution. Wash * 12345678 Non-pipelined 1|2|3|4|5|678 Pipelined 12345678 Dry 45678 + Time (a) (b) Time Fetch-instr. Decode Fetch ops. 1 2 3 4 5 6 7 8 1 2 3 4 5 6 7 8 1 2 3 4 5 6 7 8 1 2 3 4 5 6 7 8 12345678 Pipelined Execute Store res. + Time (c) fetches the next instruction. The idea of pipelining is illustrated in Figure 2.4. Note that 12:16 PM Sun Feb 28 al 22% Not Secure files.hostgator.co.in 33 of 103 2.9 Exercises 1. Describe why a general-purpose processor could cost less than a single-purpose processor you design yourself. 2. Detail the stages of executing the MOV instructions of Figure 2.4, assuming an 8-bit processor and a 16-bit IR and program memory following the model of Figure 2.1. Example: the stages for the ADD instruction are -- (1) fetch M[PC] into IR, (2) read Rn and Rm from register file through ALU configured for ADD, storing results back in Rn. 3. Add one instruction to the instruction set of Figure 2.4 that would reduce the size our summing assembly program by 1 instruction. (Hint: add a new branch instruction). Show the reduced program. 4. Create a table listing the address spaces for the following address sizes: (a) 8-bit, (b) 16-bit, (c) 24-bit, (d) 32-bit, (e) 64-bit. 5. Illustrate how program and data memory fetches can be overlapped in a Harvard architecture. 6. Read the entire problem before beginning: (a) Write a C program that clears an array "short int M[256]." In other words, the program sets every location to 0. Hint: your program should only be a couple lines long. (b) Assuming M starts at location 256 (and thus ends at location 511), write the same program in assembly language using the earlier instruction set. (c) Measure the time it takes you to perform parts a and b, and report those times. 7. Acquire a databook for a microcontroller. List the features of the basic version of that microcontroller, including key characteristics of the instruction set (number of instructions of each type, length per instruction, etc.), memory architecture andStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started