Answered step by step

Verified Expert Solution

Question

1 Approved Answer

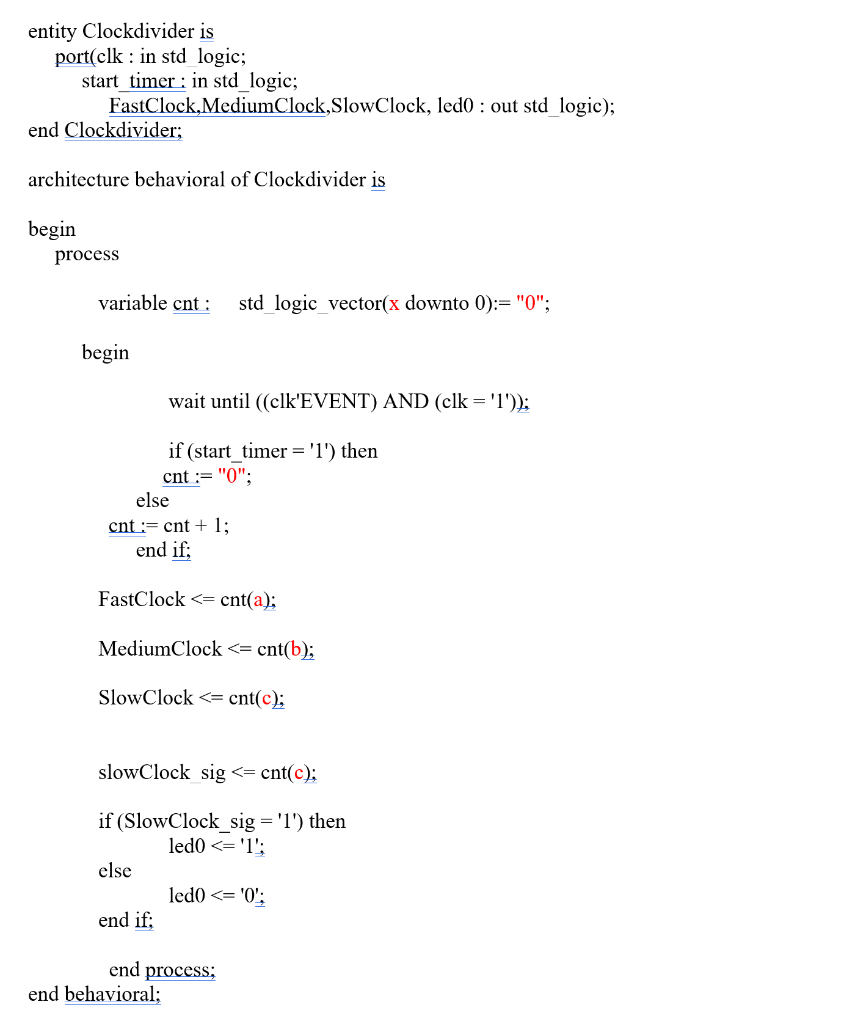

Edit the clock divider code included on the next page so that it meets the following three conditions Slowclock frequency = 1 Hz (or as

- Edit the clock divider code included on the next page so that it meets the following three conditions

- Slowclock frequency = 1 Hz (or as close as possible)

- MediumClock frequency = 2* SlowClock frequency

- FastClockFrequency = 2* MediumClock frequency

modify the portions of the code highlighted in red to divide your clock.

modify the portions of the code highlighted in red to divide your clock.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started