Answered step by step

Verified Expert Solution

Question

1 Approved Answer

in Verilog In this part you will connect the ALU with the RAM to form a simple microprocessor. Clocking the register file The register file

in Verilog

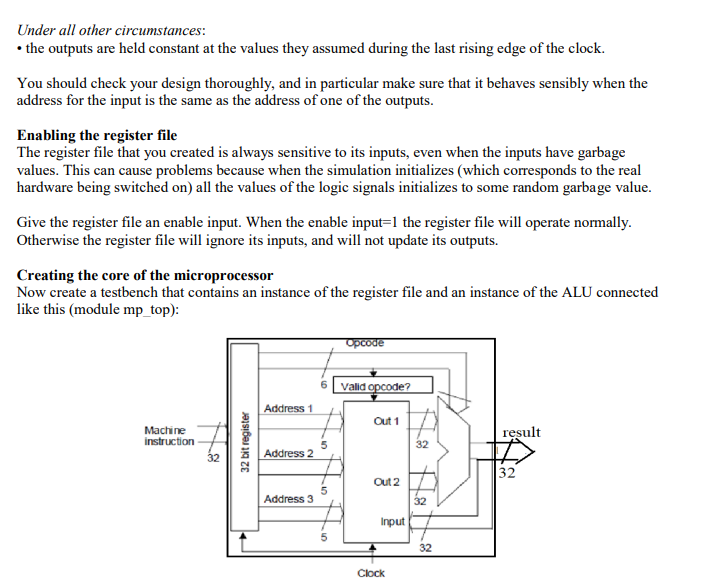

In this part you will connect the ALU with the RAM to form a simple microprocessor. Clocking the register file The register file that you created in the first part was a combinational circuit. This causes some serious problems if, for example, address 2 and address 3 are the same. The circuit would read output 2 from the location referenced by address 2 , at the same time that the input is over-writing that location. These problems can be solved by synchronising the register file to a clock. You will need to add an extra input named clock, and give the register file the following behaviour: On the rising edge of the clock: - Output 1 produces the item within the register file that is address by Address 1 . - Output 2 produces the item within the register file that is address by Address 2. - Input is used to supply a value that is written into the location addressed by Address 3. Under all other circumstances: - the outputs are held constant at the values they assumed during the last rising edge of the clock. You should check your design thoroughly, and in particular make sure that it behaves sensibly when the address for the input is the same as the address of one of the outputs. Enabling the register file The register file that you created is always sensitive to its inputs, even when the inputs have garbage values. This can cause problems because when the simulation initializes (which corresponds to the real hardware being switched on) all the values of the logic signals initializes to some random garbage value. Give the register file an enable input. When the enable input=1 the register file will operate normally. Otherwise the register file will ignore its inputs, and will not update its outputs. Creating the core of the microprocessor Now create a testbench that contains an instance of the register file and an instance of the ALU connected like this (module mp_top): Machine instructions are supplied to this arrangement in the form of 32-bit numbers. The format of these instructions is as follows: - The first 6 bits identify the opcode - The next 5 bits identify first source register - The next 5 bits identify second source register - The next 5 bits identify destination register - The final 11 bits are unused So, for example, if you want to add the contents of register 1 and register 2 and put the result into register 3 , then the machine instruction would be as follows: - The first 6 bits supply the opcode for the add instruction - The next 5 bits would address register 1 , and the next 5 would address register 2 - The next 5 bits address register 3. - The remaining bits are unused, and should be set to zero. The enable signal to the register should go high when the opcode contains a valid value, and should be low otherwise. Test out your design by supplying machine instructions to it, and check that the operation performed is correct. Make sure you understand the timing of instructions, and in particular the relationship between the clock cycle on which the instruction occurs, and the clock cycle on which the appropriate result is written to register

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started