Question: Please answer the following questions Extra info if needed: For this exercise, assume a byte-addressable system with a total memory size of 247 bytes, with

Please answer the following questions

Extra info if needed:

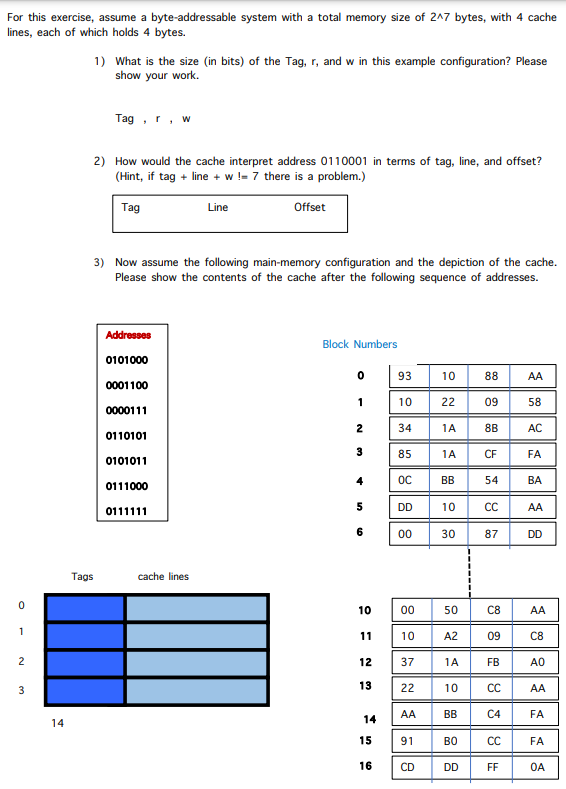

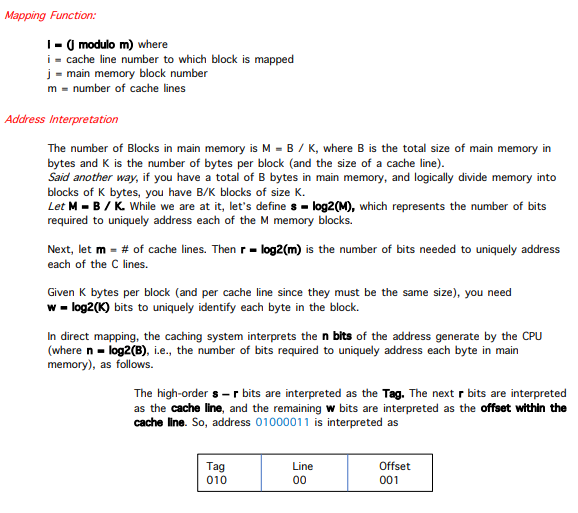

For this exercise, assume a byte-addressable system with a total memory size of 247 bytes, with 4 cache lines, each of which holds 4 bytes. 1) What is the size (in bits) of the Tag, r, and w in this example configuration? Please show your work. Tag , ! , w 2) How would the cache interpret address 0110001 in terms of tag, line, and offset? (Hint, if tag + line + w != 7 there is a problem.) Tag Line Offset 3) Now assume the following main-memory configuration and the depiction of the cache. Please show the contents of the cache after the following sequence of addresses. Block Numbers Addresses 0101000 0001100 0 93 10 88 AA 1 10 22 09 58 2 34 1A 8B AC 3 85 1A CF FA 0000111 0110101 0101011 0111000 0111111 4 OC BB 54 BA 5 DD 10 CC AA 6 00 30 87 DD Tags cache lines 0 10 00 50 C8 AA 1 11 A2 C8 10 37 2 12 1A FB AO 3 13 22 10 CC AA 14 AA BB C4 14 FA 15 91 BO CC FA 16 CD DD FF OA Mapping Function: 1 - (modulo m) where i - cache line number to which block is mapped j - main memory block number m = number of cache lines Address Interpretation The number of Blocks in main memory is M - B / K, where B is the total size of main memory in bytes and K is the number of bytes per block (and the size of a cache line). Said another way, if you have a total of B bytes in main memory, and logically divide memory into blocks of K bytes, you have B/K blocks of size K. Let M-B/K. While we are at it, let's define s - log2(M), which represents the number of bits required to uniquely address each of the M memory blocks. Next, let m = # of cache lines. Then r = log2(m) is the number of bits needed to uniquely address each of the C lines. Given K bytes per block (and per cache line since they must be the same size), you need w - log2(K) bits to uniquely identify each byte in the block. In direct mapping, the caching system interprets the n bits of the address generate by the CPU (where n- log2(B), i.e., the number of bits required to uniquely address each byte in main memory), as follows. The high-order s - bits are interpreted as the Tag. The next s bits are interpreted as the cache line, and the remaining w bits are interpreted as the offset within the cache line. So, address 01000011 is interpreted as Tag 010 Line 00 Offset 001

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts