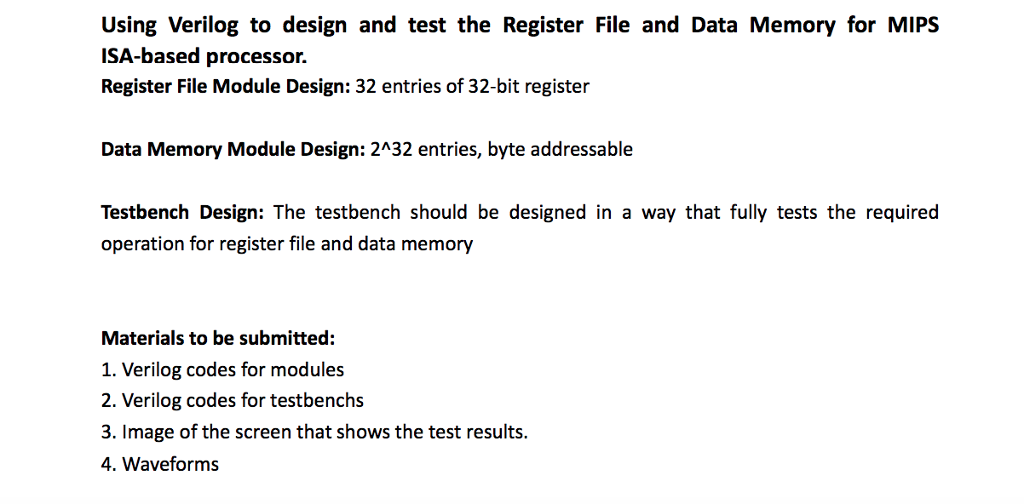

Question: Using Verilog to design and test the Register File and Data Memory for MIPS ISA-based processor. Register File Module Design: 32 entries of 32-bit register

Using Verilog to design and test the Register File and Data Memory for MIPS ISA-based processor. Register File Module Design: 32 entries of 32-bit register Data Memory Module Design: 2A32 entries, byte addressable Testbench Design: The testbench should be designed in a way that fully tests the required operation for register file and data memory Materials to be submitted: 1. Verilog codes for modules 2. Verilog codes for testbenchs 3. Image of the screen that shows the test results 4. Waveforms Using Verilog to design and test the Register File and Data Memory for MIPS ISA-based processor. Register File Module Design: 32 entries of 32-bit register Data Memory Module Design: 2A32 entries, byte addressable Testbench Design: The testbench should be designed in a way that fully tests the required operation for register file and data memory Materials to be submitted: 1. Verilog codes for modules 2. Verilog codes for testbenchs 3. Image of the screen that shows the test results 4. Waveforms

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts