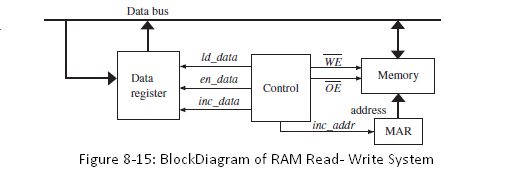

Design a memory tester that verifies the correct operation of a 6116 static RAM (Figure 8-15). The

Question:

Design a memory tester that verifies the correct operation of a 6116 static RAM (Figure 8-15). The tester should store a checkerboard pattern (alternating 0s and 1s.

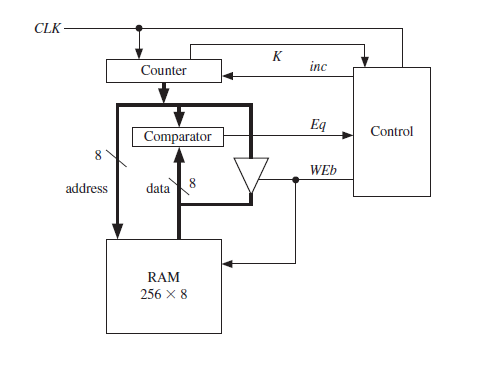

? ? ?K = 1 when counter is in state 255? ?Eq = 1 when counter output = data from memoryWEb = 0 enables tristate buffer

in the even addresses, and alternating 1s and 0s in the odd addresses) in all memory locations and then read it back. The tester should then repeat the test using the reverse pattern.(a) Draw a block diagram of the memory tester. Show and explain all control signals.(b) Draw an SM chart or state graph for the control unit. Use a simple RAM model and disregard timing.(c) Write Verilog code for the tester and use a test bench to verify its operation.

Step by Step Answer:

Digital Systems Design Using Verilog

ISBN: 978-1285051079

1st edition

Authors: Charles Roth, Lizy K. John, Byeong Kil Lee